### **Description**

PSC5415E is a switch-mode charging IC with maximum 1.75A current for lithium battery and lithium polymer battery. The PSC5415E has 5V, 700mA OTG function, and I2C function. The charging parameter such as charging current, full charging voltage and input current can be precisely configured by I2C function. The package type is WLCSP (1.901mmx1.501mm) with 20 pins.

The PSC5415E is designed with standard four-stage charging process: active, pre-charging, constant current, constant voltage and perfect protection mechanism for over current, over voltage, under voltage and over temperature. It is integrated with synchronous PWM control, high power MOSFET, and high voltage OVP circuits. The PSC5415E has high charging efficiency (94%), low internal resistance (45mΩ), and high DC withstand voltage (29V).

#### **Feature**

- Fully Integrated, High-Efficiency Charger for Single-Cell

Li-lon and Li-Polymer Battery Packs

- ➤ Charge Voltage Accuracy: ±0.5% 25°C

- ▶ ±5% Charge Current Regulation Accuracy

- 29V Absolute Maximum Input Voltage

- 5.75V Maximum Input Operating Voltage

- 1.75A Maximum Charge Rate

- 5V, 700mA Boost Mode for USB OTG for 3.0 to 4.5V Battery Input

- > 1.901 mm x 1.501mm 20-Pin WCSP Package

- Programmable through I<sup>2</sup>C Interface:

- -Input Current

- -Fast-Charge/Termination Current

- -Charger Voltage

- -Termination Enable

- Synchronous Buck PWM Controller with Wide Duty Cycle Range

- Small Footprint 1µH External Inductor

- Perfect protection mechanism:

- -OVP, OCP, OTP

### **Application**

- Cellular Phones, Smart Phones, PDAs

- > Tablet, Portable Media Players

- Gaming Device, Digital Cameras

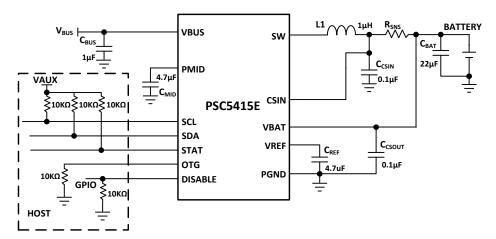

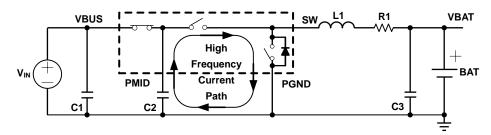

Figure 1: Typical Application

Rev.06.3 1 www.prisemi.com

## **Recommended External Components**

| Key Components   | Recommended specification             |

|------------------|---------------------------------------|

| L1               | Inductor, 1.0-2.2uH, +/-20%, Isat>3A  |

| C <sub>MID</sub> | Capacitor, 4.7μF, +/-10%, >6V         |

| C                | Capacitor, 2.2µF, +/-10%, >10V ,0402  |

| C <sub>REF</sub> | or Capacitor, 4.7µF, +/-10%, >6V,0402 |

| C <sub>BUS</sub> | Capacitor, 1µF, +/-10%, >25V          |

## **Block Diagram**

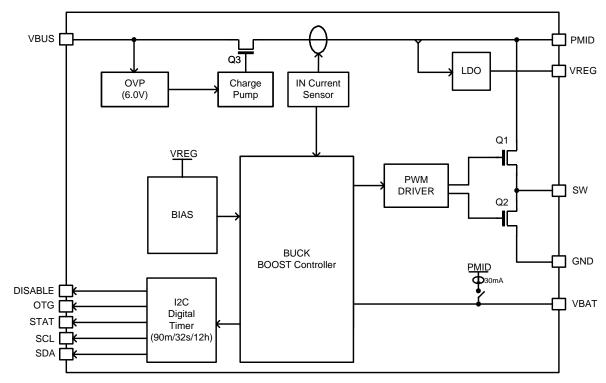

Figure 2: IC and System Block Diagram

## **Marking Information**

P15E:PSC5415E

XXXXX: Production Tracing Code

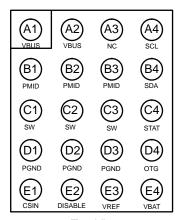

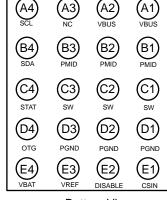

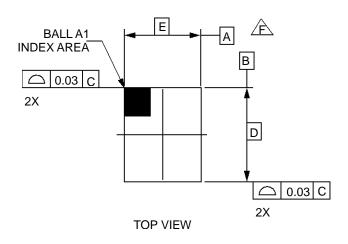

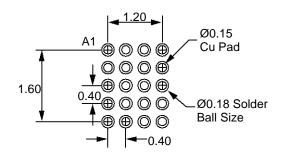

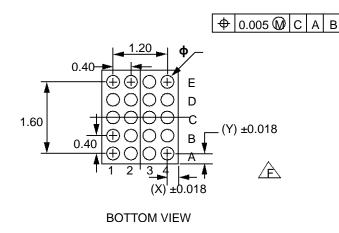

# Pin Configuration

Top View

Bottom View

Figure 3: WLCSP-20 Pin Assignments

## Pin Definitions

| Pin#  | Name    | Description                                                                                                                                                                                       |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1,A2 | VBUS    | Charger Input Voltage and USB-OTG output voltage. Bypass with 1µF capacitor to PGND                                                                                                               |

| A3    | NC      | NC.                                                                                                                                                                                               |

| A4    | SCL     | I <sup>2</sup> C Interface Serial Clock. This pin should not be left floating.                                                                                                                    |

| B1-B3 | PMID    | <b>Power Input Voltage.</b> Power input to the charger regulator, bypass point for the input current sense, and high-voltage input switch. Bypass with a minimum of 4.7μF, 10V capacitor to PGND. |

| B4    | SDA     | I <sup>2</sup> C Interface Serial Data. This pin should not be left floating.                                                                                                                     |

| C1-C3 | SW      | Switching Node. Connect to output inductor.                                                                                                                                                       |

| C4    | STAT    | Status. Open-drain output indicating charge status. The IC pulls this pin LOW when charge is in process.                                                                                          |

| D1-D3 | PGND    | <b>Power Ground.</b> Power return for gate drive and power transistors. The connection from this pin to the bottom of CMID should be as short as possible.                                        |

| D4    | OTG     | On-The-Go. Enables boost regulator in conjunction with OTG_EN and OTG_PL bits                                                                                                                     |

| E1    | CSIN    | Current-Sense Input. Connect to the sense resistor in series with the battery. The IC uses this node to sense current into the battery. Bypass this pin with a 0.1µF capacitor to PGND.           |

| E2    | DISABLE | <b>Charge Disable.</b> If this pin is "1", charging is disabled. When LOW, charging is controlled by I2C registers.                                                                               |

| E3    | VREF    | <b>Bias voltage.</b> Connect to a <b>4.7uF</b> capacitor to PGND. The output voltage is PMID, which is limited to 6.5V. Any resistor loading to VREF is <b>NOT</b> recommended.                   |

| E4    | VBAT    | Battery Voltage. Connect to the positive (+) terminal of the battery pack. Bypass with a 0.1µF capacitor to PGND if the battery is connected through long leads.                                  |

### Maximum Ratings and Thermal Characteristics(T<sub>A</sub>=25<sup>°</sup>C unless otherwise noted)

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

|                            | Parameter                                                      | Symbol            | Min.               | Max.       | Units      |

|----------------------------|----------------------------------------------------------------|-------------------|--------------------|------------|------------|

| \/PLIS \/oltogo            | Continuous                                                     | V                 | -0.7               | 29.0       | V          |

| VBUS Voltage               | Pulsed,100ms Maximum Non-Repetitive                            | $V_{BUS}$         | -1.0               | 29.0       | V          |

| STAT Voltage               |                                                                | V <sub>STAT</sub> | -0.3               | 7.0        | V          |

| PMID Voltage               |                                                                | Vı                |                    | 7.0        | V          |

| SW,CSIN,VBAT,VREF, DIS     | SW,CSIN,VBAT,VREF, DISABLE Voltage                             |                   |                    | 7.0        | V          |

| Voltage on Other Pins      | Vo                                                             | -0.3              | 6.5 <sup>(1)</sup> | V          |            |

| Maximum VBUS Slope abov    | Maximum VBUS Slope above 5.5V when Boost or Charger are Active |                   |                    | 4          | V/µs       |

| Electrostatic Discharge    | Human Body Model per JESD22-A114                               | ESD               | 20                 | 00         | V          |

| Protection Level           | Charged Device Model per JESD22-C101                           | ESD               | 50                 | 00         | V          |

| Junction Temperature       | TJ                                                             | -40               | +150               | $^{\circ}$ |            |

| Storage Temperature        | T <sub>STG</sub>                                               | -65               | +150               | $^{\circ}$ |            |

| Lead Soldering Temperature | Lead Soldering Temperature, 10 Seconds                         |                   |                    | +260       | $^{\circ}$ |

Note(1): Lesser of 6.5V or  $V_1 + 0.3V$ .

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Prisemi does not recommend exceeding them or designing to absolute maximum ratings.

| Parameter                                              | Symbol               | Min.                            | Max. | Units      |            |

|--------------------------------------------------------|----------------------|---------------------------------|------|------------|------------|

| Supply Voltage                                         | V <sub>BUS</sub>     | 4.5                             | 5.75 | V          |            |

| Maximum Battery Voltage when Boost enabled             | $V_{BAT(MAX)}$       |                                 | 4.5  | V          |            |

| Negative VBUS Slew Rate during VBUS Short Circuit,     | T <sub>A</sub> ≤60°C | - <mark>dV<sub>BUS</sub></mark> |      | 4          | V/µs       |

| C <sub>MID</sub> ≤ 22μF, see VBUS Short While Charging | T <sub>A</sub> ≥60°C | - dt                            |      | 2          | ν/μ5       |

| Ambient Temperature                                    | T <sub>A</sub>       | -30                             | +85  | $^{\circ}$ |            |

| Junction Temperature (see Thermal Protection section)  | )                    | TJ                              | -30  | +140       | $^{\circ}$ |

### **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_A$ .

| Parameter                              | Symbol        | Typical | Units |

|----------------------------------------|---------------|---------|-------|

| Junction-to-Ambient Thermal Resistance | $\theta_{JA}$ | 85      | °C/W  |

| Junction-to-PCB Thermal Resistance     | $\theta_{JB}$ | 55      | °C/W  |

### Electrical characteristics per line@25°C (unless otherwise specified)

Unless otherwise specified: according to the circuit of Figure 1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}$ =5.0V;  $HZ_MODE$ ;  $OPA_MODE$ =0; (Charge Mode); SCL, SDA, OTG=0 or 1.8V; and typical values are for  $T_J$ =25°C.

| Parameter                                         | Symbol             | Conditions                                                                                                             | Min.  | Тур. | Max.  | Units |

|---------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Power Supplies                                    |                    |                                                                                                                        |       |      |       |       |

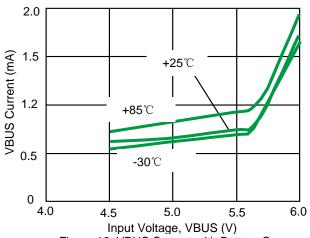

|                                                   |                    | V <sub>BUS</sub> >V <sub>BUS(MIN)</sub> , PWM Switching                                                                |       | 1.5  | 10    | mA    |

| VBUS Current                                      | I <sub>VBUS</sub>  | V <sub>BUS</sub> >V <sub>BUS</sub> (MIN); PWM Enabled,<br>Not Switching (Battery OVP<br>Condition); I_IN Setting=100mA |       | 1.2  | 10    | mA    |

| VBAT to VBUS Leakage Current                      | $I_{LKG}$          | 0°C <t<sub>J&lt;85°C<br/>V<sub>BAT</sub>=4.2V,V<sub>BUS</sub>=0V</t<sub>                                               |       | 0.2  | 1     | μΑ    |

| Battery Discharge Current in High-Impedance Mode  | I <sub>BAT</sub>   | 0℃ <t<sub>J&lt;85℃<br/>V<sub>BAT</sub>=4.2V</t<sub>                                                                    |       | 5    | 10    | μΑ    |

| Charger Voltage Regulation                        |                    |                                                                                                                        |       |      |       |       |

| Charge Voltage Range                              |                    |                                                                                                                        | 4.1   |      | 4.40  | V     |

| Chause Valtere Assures                            | $V_{OREG}$         | T <sub>J</sub> =25℃                                                                                                    | -0.5% |      | +0.5% |       |

| Charge Voltage Accuracy                           |                    | TJ=0~125℃                                                                                                              | -1%   |      | 1%    |       |

| Charging Current Regulation                       |                    |                                                                                                                        |       |      |       |       |

| Output Charge Current Range                       | 1                  | $V_{LOWV} < V_{BAT} < V_{OREG}$<br>$V_{BUS} > V_{SLP}, R_{SENSE} = 56m\Omega$                                          | 595   |      | 1750  | mA    |

| Charge Current Accuracy Across R <sub>SENSE</sub> | l <sub>OCHRG</sub> | TJ<85℃,VBAT=3.8V                                                                                                       | 92.5  | 100  | 107.5 | %     |

| Parameter                           | Symbol                  | Conditions                                                                                     | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|

| Logic Levels: DISABLE, SDA, SCL, C  | TG                      |                                                                                                |      |      |      |       |

| High-Level Input Voltage            | V <sub>IH</sub>         |                                                                                                | 1.2  |      |      | V     |

| Low-Level Input Voltage             | V <sub>IL</sub>         |                                                                                                |      |      | 0.4  | V     |

| Input Bias Current                  | I <sub>IN</sub>         | Input Tied to GND or V <sub>IN</sub>                                                           |      | 0.01 | 1.00 | μA    |

| Charge Termination Detection        |                         |                                                                                                |      |      |      |       |

| Termination Current Range           | I <sub>(TERM)</sub>     | V <sub>BAT</sub> > V <sub>OREG</sub> - V <sub>RCH</sub><br>V <sub>BUS</sub> > V <sub>SLP</sub> | 69   |      | 230  | mA    |

| Wake-up voltage                     |                         |                                                                                                |      |      |      |       |

| Wake-up voltage Range               | V <sub>wakeup</sub>     | Soft start current if vbat is lower                                                            | 3.0  | 3.15 | 3.3  | V     |

| Wake-up current                     | I <sub>wakeup</sub>     | than V <sub>wakeup</sub> (Rsense=56mΩ)                                                         |      | 352  |      | mA    |

| Input Power Source Detection        |                         |                                                                                                |      |      |      |       |

| VBUS Input Voltage Rising           | V <sub>IN(MIN)1</sub>   | To Initiate and Pass VBUS Validation                                                           |      | 4.29 | 4.42 | V     |

| Minimum VBUS during Charge          | V <sub>IN(MIN)2</sub>   | During Charging                                                                                |      | 4.1  | 4.15 | V     |

| VBUS Validation Time                | t <sub>VBUS_VALID</sub> |                                                                                                |      | 25   |      | ms    |

| Special Charger (V <sub>BUS</sub> ) |                         |                                                                                                |      |      |      |       |

| Special Charger Setpoint            | $V_{SP}$                | VSP[2:0]=100                                                                                   |      | 4.52 |      | V     |

| Special Charger Setpoint Accuracy   |                         |                                                                                                | -3   |      | +3   | %     |

| Input Current Limit                 |                         |                                                                                                |      |      |      |       |

| Input Current Limit Threshold       | I <sub>INLIM</sub>      | I <sub>IN</sub> Set to 500mA                                                                   |      | 480  |      | mA    |

| Parameter                                                          | Symbol                 | Conditions                                                        | Min. | Тур. | Max. | Units  |

|--------------------------------------------------------------------|------------------------|-------------------------------------------------------------------|------|------|------|--------|

| Battery Recharge Threshold                                         |                        |                                                                   |      |      |      |        |

| Recharge Threshold                                                 | V <sub>RCH</sub>       | Below V <sub>(OREG)</sub>                                         |      | 140  | 200  | mV     |

| STAT Output                                                        |                        |                                                                   |      |      |      |        |

| STAT Output Low                                                    | V <sub>STAT(OL)</sub>  | I <sub>STAT</sub> =10mA                                           |      |      | 0.4  | V      |

| STAT High Leakage Current                                          | I <sub>STAT(OH)</sub>  | V <sub>STAT</sub> =5V                                             |      |      | 1    | μA     |

| Sleep Comparator                                                   |                        |                                                                   |      |      |      |        |

| Sleep-Mode Entry Threshold,<br>V <sub>BUS</sub> – V <sub>BAT</sub> | $V_{SLP}$              | V <sub>BUS</sub> Falling                                          |      | 0.25 |      | V      |

| Power Switches (see Figure 2)                                      |                        |                                                                   |      |      |      |        |

| Q3 On Resistance (VBUS to PMID)                                    |                        | I <sub>IN(LIMIT)</sub> =500mA                                     |      | 40   | 60   |        |

| Q1 On Resistance (PMID to SW)                                      | R <sub>DS(ON)</sub>    |                                                                   |      | 50   | 75   | mΩ     |

| Q2 On Resistance (SW to GND)                                       |                        |                                                                   |      | 55   | 80   |        |

| Charger PWM Modulator                                              |                        |                                                                   |      |      |      |        |

| Oscillator Frequency                                               | f <sub>SW1</sub>       |                                                                   | 1.25 | 1.5  | 1.65 | MHz    |

| Oscillator Frequency                                               | f <sub>SW2</sub>       |                                                                   | 1.65 | 2.0  | 2.3  | IVITIZ |

| Maximum Duty Cycle                                                 | D <sub>MAX</sub>       |                                                                   |      |      | 97   | %      |

| Minimum Duty Cycle                                                 | D <sub>MIN</sub>       |                                                                   |      | 0    |      | %      |

| Boost Mode Operation (OPA_MODE:                                    | =1, HZ_MOD             | DE=0)                                                             |      |      |      |        |

| Boost Output Voltage at VBUS                                       | V <sub>BOOST</sub>     | 3.3V <v<sub>BAT&lt;4.5V, I<sub>LOAD</sub> from 0 to 500mA</v<sub> | 4.75 | 5.05 | 5.3  | V      |

| Boost Mode Quiescent Current                                       | I <sub>BAT(BOOST</sub> | PFM Mode, V <sub>BAT</sub> =3.6V, I <sub>OUT</sub> =0             |      | 1.6  | 10   | mA     |

| Minimum Battery Voltage for Boost<br>Operation                     | UVLO <sub>BST</sub>    |                                                                   |      | 3.0  |      | V      |

| Parameter                       | Symbol               | Conditions                            | Min. | Тур. | Max. | Unit       |

|---------------------------------|----------------------|---------------------------------------|------|------|------|------------|

| VBUS Load Resistance            |                      |                                       |      |      |      |            |

| VBUS to PGND Resistance         | R <sub>VBUS</sub>    | Normal Operation                      |      | 1500 |      | ΚΩ         |

| Protection and Timers           |                      |                                       |      |      |      |            |

| VBUS Over-Voltage Shutdown      | VDLIC                | V <sub>BUS</sub> Rising               | 5.75 | 5.9  | 6.05 | V          |

| Hysteresis                      | VBUS <sub>OVP</sub>  | V <sub>BUS</sub> Falling              |      | 150  |      | mV         |

| Battery Short-Circuit Threshold | .,                   | V <sub>BAT</sub> Rising               | 1.9  | 2.0  | 2.1  | V          |

| Hysteresis                      | V <sub>SHORT</sub>   | V <sub>BAT</sub> Falling              |      | 0.1  |      | V          |

| Linear Charging Current         | I <sub>SHORT</sub>   | V <sub>BAT</sub> < V <sub>SHORT</sub> | 20   | 30   | 40   | mA         |

| Thermal Shutdown Threshold      | т                    | T <sub>J</sub> Rising                 |      | 145  |      | $^{\circ}$ |

| Hysteresis                      | T <sub>SHUTDWN</sub> | T <sub>J</sub> Falling                |      | 10   |      | C          |

| 12H timer                       | t <sub>12H</sub>     | Charger Enabled                       |      | 12   |      | hour       |

| 90-Minute Timer                 | T <sub>90MIN</sub>   | 90-Minute Mode                        |      | 90   |      | min        |

| 32-Second Timer                 | T <sub>32s</sub>     | 32-second Mode                        |      | 32   |      | Sec        |

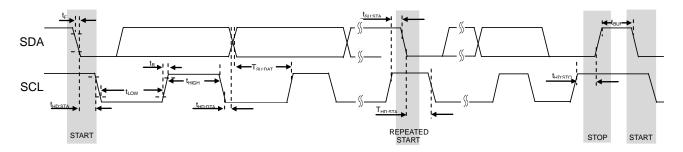

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Parameter                  | Symbol           | Conditions    | Min. | Тур. | Max. | Units |

|----------------------------|------------------|---------------|------|------|------|-------|

| SCL Clock Frequency        | f                | Standard Mode |      |      | 100  | I/U-  |

|                            | † <sub>SCL</sub> | Fast Mode     |      |      | 400  | - kHz |

| Bus-Free Time between STOP |                  | Standard Mode |      | 4.7  |      |       |

| and START Conditions       | t <sub>BUF</sub> | Fast Mode     |      | 1.3  |      | μs    |

| Parameter                                  | Symbol              | Conditions    | Min.                 | Тур.              | Max. | Units |

|--------------------------------------------|---------------------|---------------|----------------------|-------------------|------|-------|

| START or Repeated START                    |                     | Standard Mode |                      | 4                 |      | μs    |

| Hold Time                                  | t <sub>HD;STA</sub> | Fast Mode     |                      | 600               |      | ns    |

| SCL LOW Period                             | 4                   | Standard Mode |                      | 4.7               |      |       |

| SOL LOW Period                             | t <sub>LOW</sub>    | Fast Mode     |                      | 1.3               |      | μs    |

| SCL HIGH Period                            | <b>t</b>            | Standard Mode |                      | 4                 |      | μs    |

| SCL HIGH Fellou                            | t <sub>HIGH</sub>   | Fast Mode     |                      | 600               |      | ns    |

| Repeated START Setup Time                  | taa=.               | Standard Mode |                      | 4.7               |      | μs    |

| Repeated START Setup Time                  | t <sub>SU;STA</sub> | Fast Mode     |                      | 600               |      | ns    |

| Data Catura Tima                           | <b>t</b>            | Standard Mode |                      | 250               |      | ns    |

| Data Setup Time                            | t <sub>SU;DAT</sub> | Fast Mode     |                      | 100               |      | 115   |

| Data Hold Time                             | t                   | Standard Mode | 0                    |                   | 3.45 | μs    |

| Data Hold Time                             | t <sub>HD;DAT</sub> | Fast Mode     | 0                    |                   | 900  | ns    |

| SCL Rise Time                              | 4                   | Standard Mode | 20+0                 | ).1C <sub>B</sub> | 1000 | 20    |

| SCL Rise Time                              | t <sub>RCL</sub>    | Fast Mode     | 20+0                 | ).1C <sub>B</sub> | 300  | ns    |

| SCL Fall Time                              | 4                   | Standard Mode | 20+0                 | ).1C <sub>B</sub> | 300  | ns    |

| SOL Fall Tillle                            | t <sub>FCL</sub>    | Fast Mode     | 20+0                 | ).1C <sub>B</sub> | 300  | 115   |

| SDA Rise Time<br>Rise Time of SCL after a  | t <sub>RDA</sub>    | Standard Mode | 20+0.1C <sub>B</sub> |                   | 1000 | ns    |

| Repeated START Condition and after ACK Bit | t <sub>RCL1</sub>   | Fast Mode     | 20+0                 | ).1C <sub>B</sub> | 300  | 113   |

| Parameter                    | Symbol              | Conditions    | Min.                 | Тур. | Max. | Units |

|------------------------------|---------------------|---------------|----------------------|------|------|-------|

| SDA Fall Time                | 4                   | Standard Mode | 20+0.1C <sub>B</sub> |      | 300  | 20    |

|                              | t <sub>FDA</sub>    | Fast Mode     | 20+0.1C <sub>B</sub> |      | 300  | ns    |

| Stop Condition Setup Time    | t <sub>su;sto</sub> | Standard Mode |                      | 4    |      | μs    |

|                              |                     | Fast Mode     |                      | 600  |      | ns    |

| Capacitive Load for SDA, SCL | Св                  |               |                      |      | 400  | pF    |

Figure 4. I<sup>2</sup>C Interface Timing for Fast and Slow Modes

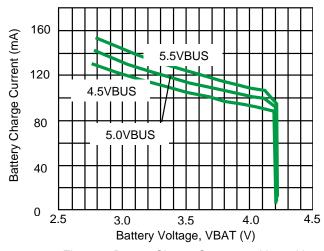

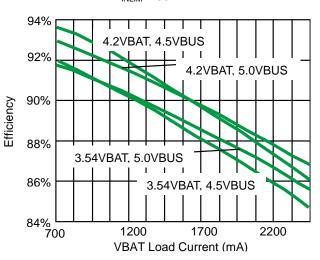

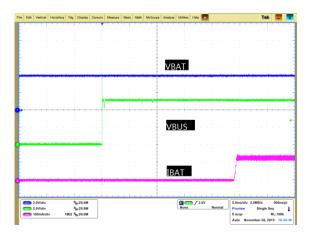

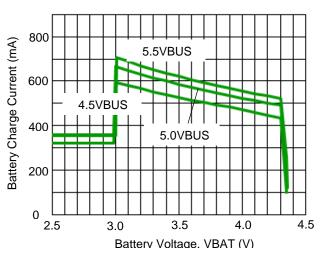

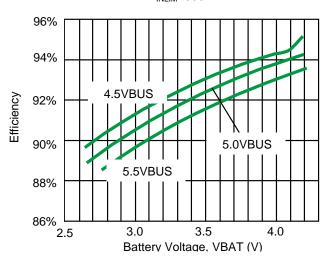

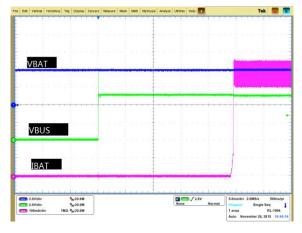

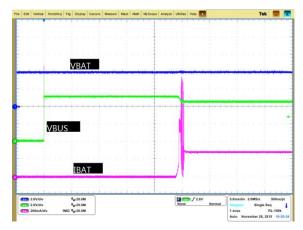

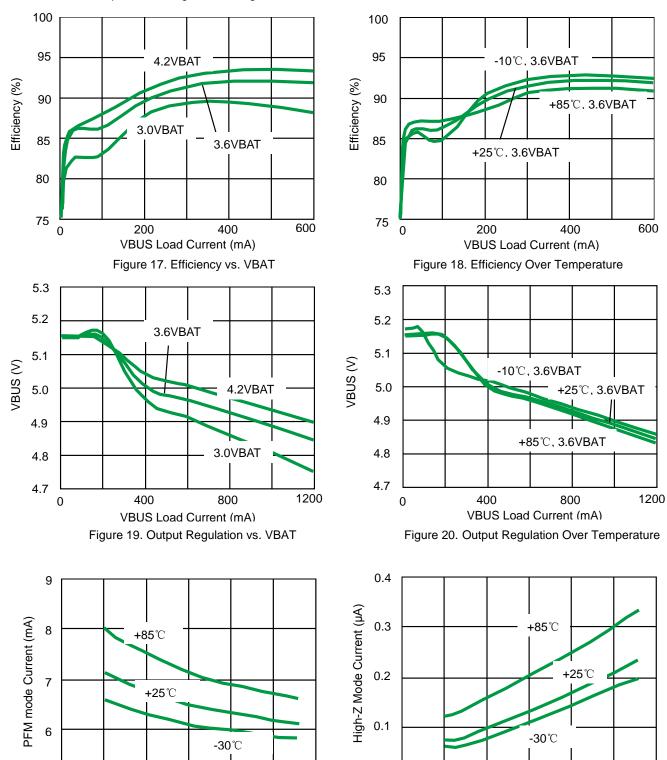

### **Charge Mode Typical Characteristics**

Unless otherwise specified, circuit of Figure 1, V<sub>OREG</sub>=4.35V, V<sub>BUS</sub>=5.0V, and T<sub>A</sub>=25℃.

Figure 5. Battery Charge Current vs.  $V_{BUS}$  with  $I_{INLIM}$ =100mA

Figure 7. Charger Efficiency, No I<sub>INLIM</sub>, I<sub>OCHARGE</sub>=2253mA

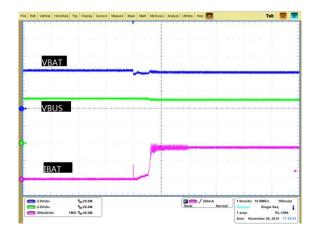

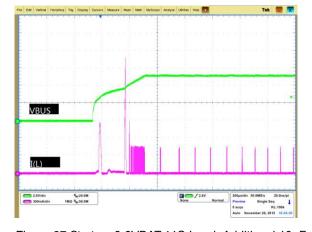

Figure 9. Auto-Charge Startup at  $V_{BUS}$  Plug-in,  $I_{INLIM}$ =100mA,  $V_{BAT}$ =3.9V

Figure 6. Battery Charge Current vs. V<sub>BUS</sub> with I<sub>INLIM</sub>=500mA

Figure 8. Charger Efficiency vs.  $V_{\text{BUS}}$ ,  $I_{\text{INLIM}}$ =500mA

Figure 10. Auto-Charge Startup at  $V_{BUS}$  Plug-in,  $I_{INLIM}$ =500mA,  $V_{BAT}$ =3.9V

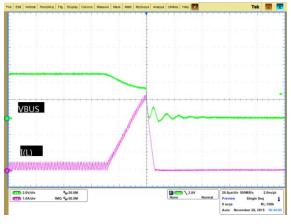

Figure 11. Auto-Charge Startup with 300mA Limited Charger/Adaptor, I<sub>INLIM</sub>=500mA, V<sub>BAT</sub>=3.9V

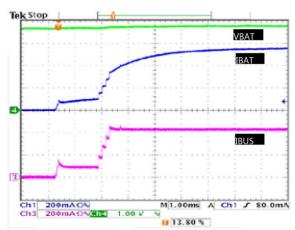

Figure 13. Battery Removal / Insertion during Charging,  $V_{BAT}\!\!=\!\!3.9V,\,I_{OCHARGE}\!\!=\!\!956mA,\,No\,\,I_{INLIM},\,TE\!=\!0$

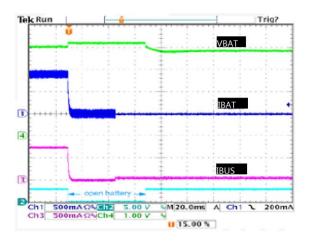

Figure 15. No Battery at V<sub>BUS</sub> Power-up

Figure 12. Charger Startup with HZ\_MODE Bit Reset, I<sub>INLIM</sub>=500mA, I<sub>OCHARGE</sub>=956mA, OREG=4.2V, V<sub>BAT</sub>=3.6V

Figure 14. Battery Removal / Insertion during Charging,  $V_{\text{BAT}}\!=\!3.9\text{V, }I_{\text{OCHARGE}}\!=\!956\text{mA, No }I_{\text{INLIM}},\,\text{TE=1}$

Figure 16. VBUS Current with Battery Open

5

2

Battery Voltage, VBAT (V)

# USB-Compliant Single-Cell Li-Ion Switching Charger with USB-OTG Boost Regulator

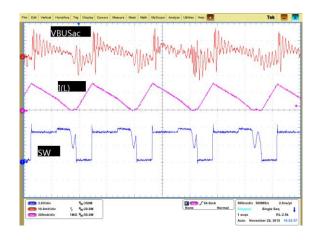

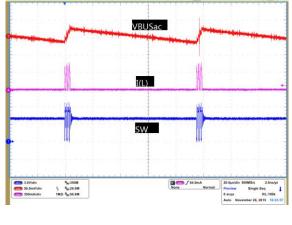

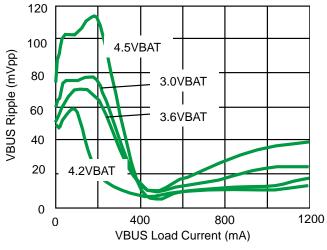

## **Boost Mode Typical Characteristics**

Unless otherwise specified, using circuit of Figure 1, V<sub>BAT</sub>=3.6V, T<sub>A</sub>=25℃.

Figure 21. PFM mode Current Figure 22. High-Impedance Mode Battery Current

2

3 4 Battery Voltage, VBAT (V) 5

0.0

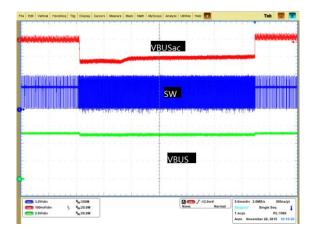

Figure 23. Boost PWM Waveform

Figure 24. Boost PFM Waveform

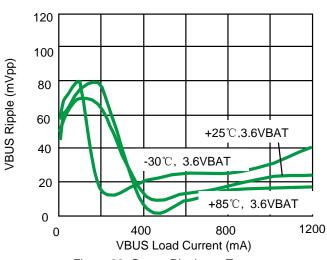

Figure 25. Output Ripple vs. VBAT

Figure 26. Output Ripple vs. Temperature

Figure 27.Startup, 3.6VBAT,44 $\Omega$  Load, Additional 10 $\mu$ F, X5R Across VBUS

Figure 28. VBUS Fault Response, 3.6VBAT

Figure 29. Load Transient, 1-150-1mA, t<sub>R</sub>=t<sub>F</sub>=100ns

### **Circuit Description/ Overview**

When charging batteries with a current-limited input source, such as USB, a switching charger's high efficiency over a wide range of output voltages minimizes charging time.

PSC5415E combines a highly integrated synchronous buck regulator for charging with a synchronous boost regulator, which can supply 5V to USB On-The-Go (OTG) peripherals. The regulator employs synchronous rectification for both the charger and boost regulators to maintain high efficiency over a wide range of battery voltages and charge states.

The PSC5415E has three operating modes:

1. Charge Mode (VBUS is valid.):

Charge a single-cell Li-ion or Li-polymer battery.

2. Boost Mode:

Provide 5V power to USB-OTG with an integrated synchronous rectification boost regulator using the battery as input.

3. Standby mode (VBUS is not valid.)

Current flow from VBUS to the battery or from the battery to VBUS is blocked.

- 1) If HZ\_MODE=0, boost can be turned on thru I2C.

- 2) If HZ\_MODE=1, boost is always off.

Note: Default settings are denoted by bold typeface.

### **Charge Mode**

In Charge Mode, PSC5415E employs four regulation loops:

- 1. Input Current: Limits the amount of current drawn from VBUS. This current is sensed internally and can be programmed through the I<sup>2</sup>C interface.

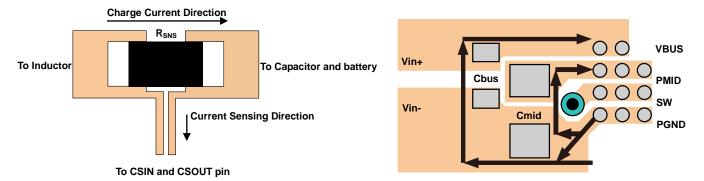

- 2. Charging Current: Limits the maximum charging current. This current is sensed using an external R<sub>SENSE</sub> resistor.

- 3. Charge Voltage: The regulator is restricted from exceeding this voltage. As the internal battery voltage rises, the battery's internal impedance and R<sub>SENSE</sub> work in conjunction with the charge voltage regulation to decrease the amount of current flowing to the battery. Battery charging is completed when the charging current drops below the I<sub>TERM</sub> threshold.

- 4. Input Voltage: PSC5415E employ an additional loop to limit the amount of drop on VBUS to a programmable voltage (V<sub>SP</sub>) to accommodate "special chargers" that limit current to a lower current than might be available from a "normal" USB wall charger.

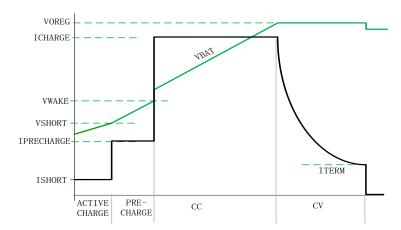

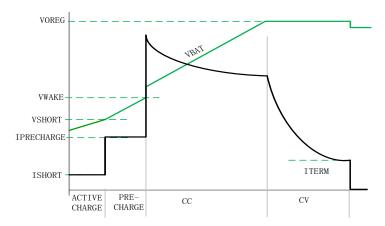

#### **Battery Charging Curve**

If the battery voltage is below  $V_{SHORT}$ , a linear current source pre-charges the battery until  $V_{BAT}$  reaches  $V_{SHORT}$ . The PWM charging circuit is then started and the battery is charged with a constant current if sufficient input power is available. The current slew rate is limited to prevent overshoot.

The PSC5415E is designed to work with a current-limited input source at VBUS. During the current regulation phase of charging, I<sub>INLIM</sub> or the programmed charging current limits the amount of current available to charge the battery and power the system. The effect of I<sub>INLIM</sub> on I<sub>CHARGE</sub> can be seen in Figure 31.

Figure 30. Charge Curve,  $I_{\text{CHARGE}}$  Not Limited by  $I_{\text{INLIM}}$

Figure 31. Charge Curve, I<sub>INLIM</sub> Limits I<sub>CHARGE</sub>

Assuming that V<sub>OREG</sub> is programmed to the cell's fully charged "float" voltage, the current that the battery accepts with the PWM regulator limiting its output (sensed at VBAT) to V<sub>OREG</sub> declines, and the charger enters the voltage regulation phase of charging. When the current declines to the programmed I<sub>TERM</sub> value, the charge cycle is complete. Charge current termination can be disabled by resetting the TE bit (REG1[3]).

The charger output or "float" voltage can be programmed by the OREG bits from 4.1V to 4.4V as shown in Table 1.

Table 1. OREG Bits (OREG[7:2]) vs. Charger V<sub>OUT</sub> (V<sub>OREG</sub>) Float Voltage

| Decimal | Hex   | VOREG |

|---------|-------|-------|

| 0-1     | 00-01 | 4.10  |

| 2-35    | 02-23 | 4.20  |

| 36-44   | 24-2C | 4.35  |

| 45-62   | 2D-3E | 4.40  |

The following charging parameters can be programmed by the host through I<sup>2</sup>C:

**Table 2. Programmable Charging Parameters**

| Parameter                      | Name               | Register  |

|--------------------------------|--------------------|-----------|

| Output Voltage Regulation      | V <sub>OREG</sub>  | REG2[7:2] |

| Battery Charging Current Limit | I <sub>OCHRG</sub> | REG4[6:4] |

| Input Current Limit            | I <sub>INLIM</sub> | REG1[7:6] |

| Charge Termination Limit       | I <sub>TERM</sub>  | REG4[2:0] |

| Weak Battery Voltage           | $V_{LOWV}$         | Reserved. |

A new charge cycle begins when one of the following occurs:

➤ The battery voltage falls below V<sub>OREG</sub>-V<sub>RCH</sub>

### Charge Current Limit (I<sub>OCHARGE</sub>) & Termination Current Limit

Table 3. IOCHARGE (REG4 [6:4]) Current as Function of IOCHARGE Bits and RSENSE Resistor Values

| DEC | DEC BIN HEX V <sub>RSENSE</sub> | \/ (m\/) | I <sub>OCHARGE</sub> (mA) |      |      |

|-----|---------------------------------|----------|---------------------------|------|------|

| DEC | DIN                             | ПЕХ      | V <sub>RSENSE</sub> (mV)  | 68mΩ | 56mΩ |

| 0   | 000                             | 00       | 32.8                      | 482  | 586  |

| 1   | 001                             | 01       | 39.3                      | 578  | 702  |

| 2   | 010                             | 02       | 52.4                      | 771  | 936  |

| 3   | 011                             | 03       | 59.0                      | 867  | 1054 |

| 4   | 100                             | 04       | 72.1                      | 1060 | 1288 |

| 5   | 101                             | 05       | 78.7                      | 1156 | 1405 |

| 6   | 110                             | 06       | 91.8                      | 1349 | 1639 |

| 7   | 111                             | 07       | 98.3                      | 1446 | 1755 |

Table 4. Terminated (REG4 [2:0]) Current as Function of ITERM Bits and RSENSE Resistor Values

| DEC | DIN | UEV | \/ (m\/)                 | I <sub>TERM</sub> (mA) |      |  |

|-----|-----|-----|--------------------------|------------------------|------|--|

| DEC | BIN | HEX | V <sub>RSENSE</sub> (mV) | 68mΩ                   | 56mΩ |  |

| 0   | 000 | 00  | 2.5                      | 36                     | 45   |  |

| 1   | 001 | 01  | 3.8                      | 55                     | 68   |  |

| 2   | 010 | 02  | 5.0                      | 73                     | 89   |  |

| 3   | 011 | 03  | 6.3                      | 91                     | 113  |  |

| 4   | 100 | 04  | 7.5                      | 110                    | 134  |  |

| 5   | 101 | 05  | 8.8                      | 128                    | 157  |  |

| 6   | 110 | 06  | 10.0                     | 147                    | 179  |  |

| 7   | 111 | 07  | 11.3                     | 165                    | 202  |  |

Current charge termination is enabled when TE (REG1[3])=1. When charging current falls below I<sub>TERM</sub>, PWM charging stops. If the charging source is still connected, STAT changes to CHARGE DONE (10).

### **PWM Controller in Charge Mode**

The IC uses a current-mode PWM controller to regulate the output voltage and battery charge currents.

### **Safety Timer**

The charger has a time out function for wake-up charge and normal charge. For wake-up charge the internal timer is set to typically 90 minutes. After 90 minutes of charging, if Vbat is still lower than 3.1V (typical), the charger is turned OFF and will not resume operation.

For normal charging the timer is set to 12 hours.

If the charger is still operating after typical 12 hours it will be turned OFF and will resume operating only if the condition (VOREG-VBAT) >100mV is met.

The 90-min and 12-hour timer can be reset by plugging out/in the adapter.

PSC5415E also has a 32s-timer for watch-dog function which is only for OTG mode. If it does not receive any read/write command during 32s, it will be reset to default parameters and quit OTG mode.

### **VBUS POR / Non-Compliant Charger Rejection**

When VBUS is inserted, VBUS must remain above  $V_{IN(MIN)1}$  and below VBUS<sub>OVP</sub> for  $t_{VBUS\_VALID}$  (25ms) before the IC initiates charging. The VBUS validation sequence always occurs before charging is initiated or re-initiated (for example, after a VBUS OVP fault or a  $V_{RCH}$  recharge initiation).

tvbus\_valid ensures that unfiltered 50/60Hz chargers and other non-compliant chargers are rejected.

#### Input Current Limiting

To minimize charging time without overloading VBUS current limitations, the IC's input current limit can be programmed by the I<sub>INLIM</sub> bits (REG1[7:6]).

**Table 5. Input Current Limit**

| I <sub>INLIM</sub> REG1[7:6] | Input Current Limit |

|------------------------------|---------------------|

| 00                           | 150mA               |

| 01                           | 500mA               |

| 10                           | 800mA               |

| 11                           | No Limit            |

### **Special Charger**

The PSC5415E have additional functionality to limit input current in case a current-limited "special charger" is supplying VBUS. The PSC5415E slowly increases the charging current until either:

$I_{\text{INLIM}}$  or  $I_{\text{OCHARGE}}$  is reached or  $V_{\text{BUS}} = V_{\text{SP}}$

If V<sub>BUS</sub> collapses to V<sub>SP</sub> when the current is ramping up, the PSC5415E charge with an input current that keeps V<sub>BUS</sub>=V<sub>SP</sub>.

**Table 6. Input Voltage Limit**

| V <sub>SP</sub> REG5[2:0] | Input Voltage Limit (V) |

|---------------------------|-------------------------|

| 000                       | 4.214                   |

| 001                       | 4.29                    |

| 010                       | 4.366                   |

| 011                       | 4.442                   |

| 100                       | 4.52(Default)           |

| 101                       | 4.59                    |

| 110                       | 4.67                    |

| 111                       | 4.8                     |

#### **Thermal Protection**

If the temperature increases beyond T<sub>SHUTDOWN</sub>; charging is suspended, the FAULT bits are set to 101.

Note that as power dissipation increases, the effective  $\theta_{JA}$  decreases due to the larger difference between the die temperature and its ambient.

### **Charge Mode Input Supply Protection**

#### Input Supply Low-Voltage Detection

The IC continuously monitors VBUS during charging. If V<sub>BUS</sub> falls below V<sub>IN(MIN)</sub>, the IC terminates charging.

#### **Input Over-Voltage Detection**

When the VBUS exceeds VBUS<sub>OVP</sub>, the IC suspends charging

When VBUS falls about 150mV below VBUS<sub>OVP</sub>, the fault is cleared and charging resumes after VBUS is revalidated (see VBUS POR / Non-Compliant Charger Rejection).

### **Charge Mode Battery Detection & Protection**

#### **VBAT Over-Voltage Protection**

The OREG voltage regulation loop prevents VBAT from overshooting the OREG voltage by more than 50mV when the battery is removed. When the PWM charger runs with no battery, the TE bit is not set and a battery is inserted that is charged to a voltage higher than  $V_{OREG}$ ; PWM pulses stop.

### **System Operation with No Battery**

The PSC5415E continue charging after  $V_{BUS}$  POR with the default parameters, regulating the  $V_{BAT}$  line to 4.2V until the host processor issues commands. In this way, the PSC5415E can start the system without a battery.

Using following sequence is suggested:

- 1. When VBUS is plugged in, I<sub>INLIM</sub> is set to 500mA until the system processor powers up and can set parameters through I<sup>2</sup>C.

- 2. Program the Safety Register.

- 3. Set I<sub>INLIM</sub> to 11 (no limit).

- 4. Set OREG to the desired value (typically 4.2V).

- 5. Set I<sub>INLIM</sub> to 500mA if a USB source is connected.

During the initial system startup, while the charger IC is being programmed, the system current is limited to 500mA before

#### **Charger Status**

The STAT pin is for test purpose, the IC provides the charging status in REG0[5:4].

### **Operational Mode Control**

OPA\_MODE (REG1[0]) and the HZ\_MODE (REG1[1]) bits in conjunction with the DISABLE pin define the operational mode of the charger.

**Table 7. Operation Mode Control**

| HZ_ MODE | OPA_MODE | DISABLE | Operation Mode   |

|----------|----------|---------|------------------|

| X        | 0        | 0       | Charge           |

| X        | X        | 1       | Charger disabled |

| 0        | 1        | X       | Boost            |

| 1        | Х        | Х       | High Impedance   |

The IC resets the OPA\_MODE bit whenever the boost is deactivated, whether due to a fault or being disabled by setting the HZ\_MODE bit. Setting HZ\_MODE=1 through I<sup>2</sup>C won't disable charger but only disable boost function.

#### **Boost PWM Control**

The IC uses a minimum on-time and computed minimum off-time to regulate VBUS. The regulator achieves excellent transient response by employing current-mode modulation. This technique causes the regulator to exhibit a load line. During PWM Mode, the output voltage drops slightly as the input current rises. With a constant V<sub>BAT</sub>, this appears as a constant output resistance.

#### **PFM Mode**

If  $V_{BUS} > VREF_{BOOST}$  (nominally 5.15V) when the minimum off-time has ended, the regulator enters PFM Mode. Boost pulses are inhibited until  $V_{BUS} < VREF_{BOOST}$ . The minimum on-time is increased to enable the output to pump up sufficiently with each PFM boost pulse. Therefore the regulator behaves like a constant on-time regulator, with the bottom of its output voltage ripple at 5.15V in PFM Mode.

#### Startup

When the boost regulator is shut down, current flow is prevented from  $V_{BAT}$  to  $V_{BUS}$ , as well as reverse flow from  $V_{BUS}$  to  $V_{BAT}$ .

#### SS State

This IC has built-in soft start function to prevent the IC being out of control. The reference voltage is slightly raised to the normal voltage within about 50us. In SS state, peak current is limited as 1.5x of that in normal condition. When SS is done, the current limit is set to 100%.

#### **BST State**

This is the normal operating mode of the regulator. The regulator uses a minimum  $t_{\text{OFF}}$ -minimum  $t_{\text{ON}}$  modulation scheme. The minimum  $t_{\text{OFF}}$  is proportional to  $\frac{V_{\text{IN}}}{V_{\text{OUT}}}$  Which keeps the regulator's switching frequency reasonably constant in CCM.  $t_{\text{ON(MIN)}}$  is proportional to VBAT and is a higher value if the inductor current reached 0 before  $t_{\text{OFF}(MIN)}$  in the prior cycle. To ensure the VBUS does not pump significantly above the regulation point, the boost switch remains off as long as

FB > V<sub>REF</sub>.

#### **Boost Faults**

If a BOOST fault occurs:

- 1. The STAT pin pulses.

- 2. OPA\_MODE bit is reset.

- 3. The power stage is in High-Impedance Mode.

### I<sup>2</sup>C Interface

The PSC5415E's serial interface is compatible with Standard, Fast, Fast Plus, and High-Speed Mode I<sup>2</sup>C-Bus® specifications. The PSC5415E's SCL line is an input and its SDA line is a bi-directional open-drain output; it can only pull down the bus when active. The SDA line only pulls LOW during data reads and when signaling ACK. All data is shifted in MSB (bit 7) first.

#### **Slave Address**

Table 8. I<sup>2</sup>C Slave Address Byte

| Part Types | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|------------|---|---|---|---|---|---|---|-----|

| PSC5415E   | 1 | 1 | 0 | 1 | 0 | 1 | 0 | R/W |

In hex notation, the slave address assumes a 0 LSB. The hex slave address for the PSC5415E is D4H.

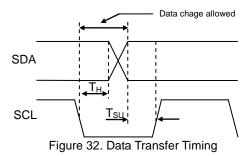

#### **Bus Timing**

As shown in Figure 32, data is normally transferred when SCL is LOW. Data is clocked in on the rising edge of SCL. Typically, data transitions shortly at or after the falling edge of SCL to allow ample time for the data to set up before the next SCL rising edge.

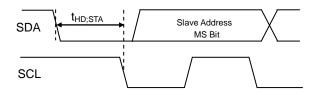

Each bus transaction begins and ends with SDA and SCL HIGH. A transaction begins with a START condition, which is defined as SDA transitioning from 1 to 0 with SCL HIGH, as shown in Figure 33.

Figure 33. Start Bit

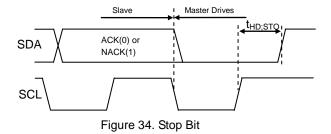

A transaction ends with a STOP condition, which is defined as SDA transitioning from 0 to 1 with SCL HIGH, as shown in Figure 34.

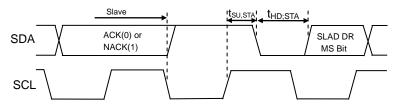

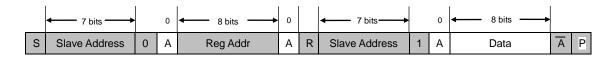

During a read from the PSC5415E (Figure 37), the master issues a Repeated Start after sending the register address and before resending the slave address. The Repeated Start is a 1-to-0 transition on SDA while SCL is HIGH, as shown in Figure 35.

Figure 35. Repeated Start Timing

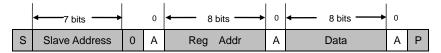

#### **Read and Write Transactions**

The figures below outline the sequences for data read and write. Bus control is signified by the shading of the packet, defined as Master Drives Bus and Slave Drives Bus

All addresses and data are MSB first.

Table 9. Bit Definitions for Figure 36, Figure 37

| Symbol | Definition                                                          |

|--------|---------------------------------------------------------------------|

| S      | START, see Figure 33                                                |

| А      | ACK. The slave drives SDA to 0 to acknowledge the preceding packet. |

| Ā      | NACK. The slave sends a 1 to NACK the preceding packet.             |

| R      | Repeated START, see Figure 35                                       |

| Р      | STOP, see Figure 34                                                 |

Figure 36. Write Transaction

Figure 37. Read Transaction

### **Register Descriptions**

Table 10. I<sup>2</sup>C Register Address

| IC       | Register   |      |   | Address Bits |   |   |   |   |   |   |

|----------|------------|------|---|--------------|---|---|---|---|---|---|

| IC       | Name       | REG# | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|          | CONTROL0   | 0    | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |

|          | CONTROL1   | 1    | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 1 |

|          | OREG       | 2    | 0 | 0            | 0 | 0 | 0 | 0 | 1 | 0 |

|          | IC_INFO    | 3    | 0 | 0            | 0 | 0 | 0 | 0 | 1 | 1 |

| PSC5415E | IBAT       | 4    | 0 | 0            | 0 | 0 | 0 | 1 | 0 | 0 |

|          | SP_CHARGER | 5    | 0 | 0            | 0 | 0 | 0 | 1 | 0 | 1 |

|          | SAFETY     | 6    | 0 | 0            | 0 | 0 | 0 | 1 | 1 | 0 |

|          | SPR        | 51   | 1 | 0            | 0 | 1 | 0 | 0 | 0 | 1 |

|          | TEST       | 10   | 0 | 0            | 0 | 1 | 0 | 0 | 0 | 0 |

### **Table 11. Register Bit Definitions**

This table defines the operation of each register bit for all IC versions. Default values are in bold text.

| Bit     | Name  | Value | Туре | Description                                 |  |  |

|---------|-------|-------|------|---------------------------------------------|--|--|

| CONTROL | .0    |       | ı    | Register Address:00 Default Value=X1XX 0XXX |  |  |

| 7:6     | -     | -     | -    | Reserved. [1]                               |  |  |

|         |       | 00    | R    | Ready                                       |  |  |

| 5.4     | STAT  | 01    |      | Charge in progress                          |  |  |

| 5:4     | SIAI  | 10    |      | Charge done                                 |  |  |

|         |       | 11    |      | Fault                                       |  |  |

| 3       | BOOST | 0     | R    | IC is not in Boost Mode                     |  |  |

| 3       | ВООЗТ | 1     |      | IC is in Boost Mode                         |  |  |

| 2:0     | -     |       | R    |                                             |  |  |

Note[1]: Any I2C operations can be used to reset 32s timer. If the 5415E is in OTG mode and does not receive any read/write command during 32s, it will be reset to default parameters and quit OTG mode.

| Bit     | Name               | Value | Туре                             | Description                                                   |                                                    |  |  |  |

|---------|--------------------|-------|----------------------------------|---------------------------------------------------------------|----------------------------------------------------|--|--|--|

| CONTRO  | DL1                |       |                                  | Register Address:01                                           | Default Value=0111 0000                            |  |  |  |

|         |                    |       | Input current limit, see Table 5 |                                                               |                                                    |  |  |  |

|         |                    |       |                                  | REG01[7:6]                                                    | Input Current Limit                                |  |  |  |

|         |                    |       |                                  | BIN                                                           | ·                                                  |  |  |  |

| 7:6     | I <sub>INLIM</sub> |       | R/W                              | 00                                                            | 150mA                                              |  |  |  |

|         |                    |       |                                  | 01                                                            | 500mA                                              |  |  |  |

|         |                    |       |                                  | 10                                                            | 800mA                                              |  |  |  |

|         |                    |       |                                  | 11                                                            | Unlimited                                          |  |  |  |

| 5:4     | VLOWV              |       | R/W                              | Reserved.                                                     |                                                    |  |  |  |

| 3       | TE                 | 0     | R/W                              | Disable charge current termina                                | ation                                              |  |  |  |

|         | 15                 | 1     | 10,77                            | Enable charge current termina                                 | tion                                               |  |  |  |

| 2       | CE                 | 0     | R/W                              | Enable charge;                                                |                                                    |  |  |  |

| 2       | OL                 | 1     | 17,77                            | Disable charge;                                               |                                                    |  |  |  |

| 4       | LIZ MODE           | 0     | DAM                              | Not High-Impedance Mode                                       |                                                    |  |  |  |

| 1       | HZ_MODE            | 1     | R/W                              | High-Impedance Mode                                           |                                                    |  |  |  |

|         | 004 14005          | 0     | D.4.4/                           | Charge Mode                                                   |                                                    |  |  |  |

| 0       | OPA_MODE           | 1     | R/W                              | Boost Mode                                                    |                                                    |  |  |  |

| OREG    |                    |       |                                  | Register Address:02                                           | Default Value=0000 0000                            |  |  |  |

|         |                    |       |                                  | Charger output "float" voltage; increments; defaults to 00000 | programmable from 4.1 to 4.4V  (4.1V), see Table 1 |  |  |  |

|         | 0050               |       | 544                              | REG02[7:2]<br>BIN                                             | VOREG                                              |  |  |  |

| 7:2     | OREG               |       | R/W                              | 000000 - 000001                                               | 4.1V                                               |  |  |  |

|         |                    |       |                                  | 000010 - 100011                                               | 4.2V                                               |  |  |  |

|         |                    |       |                                  | 100100 - 101100                                               | 4.35V                                              |  |  |  |

|         |                    |       |                                  | 101101 - 111110                                               | 4.4V                                               |  |  |  |

| 1:0     | -                  | 0     | R/W                              | -                                                             |                                                    |  |  |  |

| IC_INFO |                    |       |                                  | Register Address: 03 or 3B                                    | Default Value=1111 0XXX                            |  |  |  |

| 7:5     | Vendor Code        | 111   | R                                | Identifies Prisemi as the IC supplier                         |                                                    |  |  |  |

| 4:0     | TN                 | 10    | R                                | Product Tracking Number;                                      |                                                    |  |  |  |

| Bit  | Name     | Value   | Туре | Description                                              |            |                         |              |      |  |

|------|----------|---------|------|----------------------------------------------------------|------------|-------------------------|--------------|------|--|

| IBAT |          |         |      | Register Ad                                              | dress: 04  | Default Value=1000 1001 |              |      |  |

| 7    | RESET    | 1       | W    | Writing a 1 reset all charge parameters. Read returns 0  |            |                         |              |      |  |

| _    |          |         |      | Programs the maximum charge current, see Table 3         |            |                         |              |      |  |

|      |          | Table 3 | R/W  | REG51[0]                                                 | REG04[6:4] | - I Vrsns(mV            | Icharge (mA) |      |  |

|      |          |         |      |                                                          | BIN        |                         | 68mΩ         | 56mΩ |  |

|      |          |         |      | 0                                                        | 000        | 32.8                    | 482          | 586  |  |

|      |          |         |      |                                                          | 001        | 39.3                    | 578          | 702  |  |

|      |          |         |      |                                                          | 010        | 52.4                    | 771          | 936  |  |

|      |          |         |      |                                                          | 011        | 59                      | 867          | 1054 |  |

|      |          |         |      |                                                          | 100        | 72.1                    | 1060         | 1288 |  |

|      |          |         |      |                                                          | 101        | 78.7                    | 1156         | 1405 |  |

| 6:4  | IOCHARGE |         |      |                                                          | 110        | 91.8                    | 1349         | 1639 |  |

|      |          |         |      |                                                          | 111        | 98.3                    | 1446         | 1755 |  |

|      |          |         |      |                                                          | 000        | 26.7                    | 392          | 477  |  |

|      |          |         |      |                                                          | 001        | 33.3                    | 490          | 595  |  |

|      |          |         |      |                                                          | 010        | 40                      | 588          | 714  |  |

|      |          |         |      | 1                                                        | 011        | 46.7                    | 686          | 834  |  |

|      |          |         |      |                                                          | 100        | 53.3                    | 784          | 952  |  |

|      |          |         |      |                                                          | 101        | 60                      | 882          | 1071 |  |

|      |          |         |      |                                                          | 110        | 66.7                    | 980          | 1191 |  |

|      |          |         |      |                                                          | 111        | 86.7                    | 1275         | 1548 |  |

| 3    | -        | -       | R    | Reserved.                                                |            |                         |              |      |  |

|      |          |         |      | Programs the terminated charge-done current, see Table 4 |            |                         | le 4         |      |  |

|      | ITERM    | Table 4 | R/W  | REG04[2:0]                                               |            | ITERM (mA)              |              |      |  |

| 2:0  |          |         |      | BIN                                                      |            | Vrsns                   | 68mΩ         | 56mΩ |  |

|      |          |         |      | 000                                                      |            | 2.5                     | 36           | 45   |  |

|      |          |         |      | 001                                                      |            | 3.8                     | 55           | 68   |  |

|      |          |         |      | 010                                                      |            | 5.0                     | 73           | 89   |  |

|      |          |         |      | 011                                                      |            | 6.3                     | 91           | 113  |  |

|      |          |         |      | 100                                                      |            | 7.5                     | 110          | 134  |  |

|      |          |         |      | 101                                                      |            | 8.8                     | 128          | 157  |  |

|      |          |         |      | 110                                                      |            | 10.0                    | 147          | 179  |  |

|      |          |         |      | 111                                                      |            | 11.3                    | 165          | 202  |  |

| Bit        | Name       | Value | Туре | Description                                                                                                                  |                         |  |  |

|------------|------------|-------|------|------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| SP_CHARGER |            |       |      | Register Address: 05                                                                                                         | Default Value=001X X100 |  |  |

| 7          | ADD20MV    | 0     | R/W  | The OREG value will be increased 20mv if bit7 is set "1"; For example, 4.2 will be 4.22V if set ADD20MV=1;                   |                         |  |  |

| 6:5        | Reserved   | -     | -    | Reserved                                                                                                                     | Reserved                |  |  |

| 4          | SP         | 0     | R    | Special charger is not active (V <sub>BUS</sub> is able to stay above V <sub>SP</sub> )                                      |                         |  |  |

| 4          | <b>3</b> F | 1     |      | Special charger has been detected and V <sub>BUS</sub> is being regulated to V                                               |                         |  |  |

| 3          | EN_LEVEL   | 0     | R/W  | Reserved.                                                                                                                    |                         |  |  |

|            | VSP        | 100   | R/W  | Input voltage limit, see Table 6                                                                                             |                         |  |  |

|            |            |       |      | REG05[2:0]<br>BIN                                                                                                            | VSP (V)                 |  |  |

|            |            |       |      | 000                                                                                                                          | 4.214                   |  |  |

|            |            |       |      | 001                                                                                                                          | 4.29                    |  |  |

| 2:0        |            |       |      | 010                                                                                                                          | 4.366                   |  |  |

|            |            |       |      | 011                                                                                                                          | 4.442                   |  |  |

|            |            |       |      | 100                                                                                                                          | 4.52(default)           |  |  |

|            |            |       |      | 101                                                                                                                          | 4.59                    |  |  |

|            |            |       |      | 110                                                                                                                          | 4.67                    |  |  |

|            |            |       |      | 111                                                                                                                          | 4.8                     |  |  |

| SPR        |            |       |      | Register Address: 51                                                                                                         | Default Value=0000 0000 |  |  |

| 1          | FSE        | 0     | R/W  | 0: Choose PWM frequency 1.5Mhz; 1: Choose PWM frequency 2.0Mhz;                                                              |                         |  |  |

| 0          | ICE        | 0     | R/W  | Option for Charge current; see table 3                                                                                       |                         |  |  |

| TEST       |            |       |      | Register Address: 10                                                                                                         | Default Value=0000 0000 |  |  |

| 2:0        | TEST_STAT  | 000   | R/W  | 000: STAT output is low if VBUS is valid for charge, otherwise STAT is floating output; 111: STAT output is always floating; |                         |  |  |

### **PCB Layout Considerations**

- 1. To obtain optimal performance, the power input capacitors, connected from input to PGND, should be placed as close as possible to the pin. The output inductor should be placed close to the IC and the output capacitor connected between the inductor and PGND of the IC. The intent is to minimize the current path loop area from the SW pin through the LC filter and back to the PGND pin. To prevent high frequency oscillation problems, proper layout to minimize high frequency current path loop is critical. (See Figure 38.) The sense resistor should be adjacent to the junction of the inductor and output capacitor. Route the sense leads connected across the RSNS back to the IC, close to each other (minimize loop area) or on top of each other on adjacent layers (do not route the sense leads through a high-current path). (See Figure 39.)

- 2. Place all decoupling capacitors close to their respective IC pins and close to PGND (do not place components such that routing interrupts power stage currents). All small control signals should be routed away from the high current paths.

- 3. The PCB should have a ground plane (return) connected directly to the return of all components through vias (two vias per capacitor for power-stage capacitors, two vias for the IC PGND, one via per capacitor for small- signal components). A star ground design approach is typically used to keep circuit block currents isolated (high-power/low-power small-signal) which reduces noise-coupling and ground-bounce issues. A single ground plane for this design gives good results. With this small layout and a single ground plane, there is no ground-bounce issue, and having the components segregated minimizes coupling between signals.

- 4. The high-current charge paths into VBUS, PMID and from the SW pins must be sized appropriately for the maximum charge current in order to avoid voltage drops in these traces. The PGND pins should be connected to the ground plane to return current through the internal low-side FET.

- 5. Place 22μF input capacitor as close to PMID pin and PGND pin as possible to make high frequency current loop area as small as possible. Place 1μF input capacitor as close to VBUS pin and PGND pin as possible to make high frequency current loop area as small as possible (see Figure 40).

Figure 38. high frequency current path

Figure 39. Sensing resistor PCB layout

Figure 40. Input capacitor position and PCB layout example

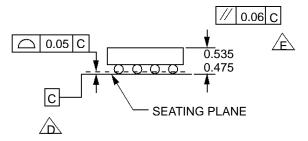

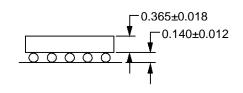

### **Product dimension**

RECOMMENDED LAND PATTERN (NSMD TYPE)

SIDE VIEWS

#### NOTES:

A.NO JEDEC REGISTRATION APPLIES.

B.DIMENSIONS ARE IN MILLIMETERS.

C.DIMENSIONS AND TOLERANCE

PER ASMER14.5M,1994.

DDATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

<u>PACKAGE NOMINAL HEIGHT IS 586 MICRONS</u> ±39 MICRONS(547-625 MICRONS).

PRODUCT DATASHEET.

G.DRAWING FILNAME: MKT-UC020AArev2.

Figure 41. 20-Ball WLCSP, 4x5 Array, 0.4mm Pitch, 150µm Ball

### **Product-Specific Dimensions (mm)**

| Product  | D           | E           | х     | Υ     | ф           |

|----------|-------------|-------------|-------|-------|-------------|

| PSC5415E | 1.901±0.030 | 1.501±0.030 | 0.150 | 0.150 | 0.150±0.020 |

## **Ordering Information**

| Device   | Package                 | Reel | Shipping           |

|----------|-------------------------|------|--------------------|

| PSC5415E | 20-Ball WLCSP (Pb-Free) | 7"   | 3000 / Tape & Reel |

#### **IMPORTANT NOTICE**

and Prisemi are registered trademarks of Prisemi Electronics Co., Ltd (Prisemi), Prisemi reserves the right to make changes without further notice to any products herein. Prisemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Prisemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in Prisemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Prisemi does not convey any license under its patent rights nor the rights of others. The products listed in this document are designed to be used with ordinary electronic equipment or devices, Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

Prisemi reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and datasheets before placing orders and should verify that such information is current and complete.

Website: http://www.prisemi.com

For additional information, please contact your local Sales Representative.

©Copyright 2009, Prisemi Electronics

Prisemi is a registered trademark of Prisemi Electronics.

All rights are reserved.