# 1. Description

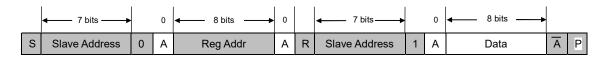

PSC2965 combines a highly integrated switch-mode charger, to minimize single-cell Lithium-ion (Li-ion) charging time from a USB power source, and a boost regulator to power a USB peripheral from the battery. Its low impedance power path optimizes switch-mode operation efficiency, reduces battery charge time and extends battery life during discharging phase. The I2C serial interface with charging and system settings makes the device a truly flexible solution.

The device supports 4.5-13.5V input voltage sources, including standard USB host port and USB charging port with programmable over-voltage protection. The device also supports USB On-the-Go operation by providing on the VBUS with an accurate current limit.

The power path management regulates the system slightly above battery voltage but does not drop below 3.55V minimum system voltage (programmable). With this feature, the system keeps operating even when the battery is completely depleted or removed. When the input source current or voltage limit is reached, the power path management automatically reduces the charge current to zero and then starts discharges the battery until the system power requirement is met. This supplement mode operation keeps the input source from getting overloaded.

The device initiates and completes a charging cycle when host control is not available. It automatically charges the battery in three phases: pre-conditioning, constant current, and constant voltage. In the end, the charger automatically terminates when the charge current is below a preset limit in the constant voltage phase. Later on, when the battery voltage falls below the recharge threshold, the charger automatically starts another charging cycle.

The charge device provides various safety features for battery charging and system operation, including charging safety timer, and over-voltage/over-current protections.

The STAT output reports the charging status. The INT output can be used to notify the host when VBUS insertion and withdrawal or a fault occurs.

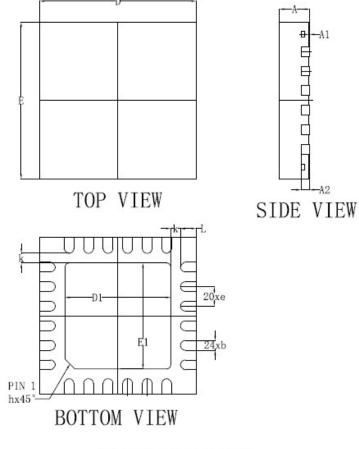

The PSC2965 is available in a 24-pin, 4mm x 4mm x 0.55mm QFN package.

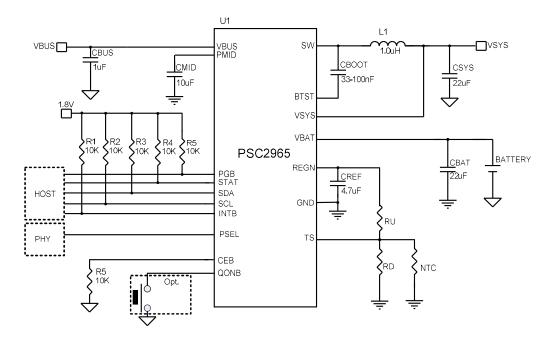

Figure 1.1 Typical Application

| Key Components | Recommended specification           |  |  |  |

|----------------|-------------------------------------|--|--|--|

| L1             | Inductor, 1.0-2.2uH, +-20%, Isat>4A |  |  |  |

| Смір           | Capacitor, 10µF , +-10%, >16V       |  |  |  |

| CREF           | Capacitor, 4.7µF, +-10%, >6V        |  |  |  |

| CBUS           | Capacitor, 1.0µF, +-10%, >16V       |  |  |  |

| Своот          | Capacitor, 100nF, +-10%, >10V       |  |  |  |

# 2. Features

Fully Integrated, High-Efficiency Switching Mode 3A Charger.

- ◆ Charge Voltage Accuracy: ±0.5% 25°C

- ±7.5% Charge Current Regulation Accuracy

- 20V Absolute Maximum Input Voltage

- 13.5V Maximum Input Operating Voltage

- Weak Input Sources Accommodated by Reducing Charging Current to Maintain Minimum VBUS Voltage

- Power Path Management

- Instant system on with NO battery or deeply discharged battery

- Battery can be completely turned off after Charging Done

- Supports Ultra low leakage ship mode

- > Programmable through I2C Interface:

- Input Current limit

# 3. Applications

- Cellular Phones, Smart Phones, PDAs

- > Tablet, Portable Media Players

- Fast-Charge/Termination Current

- Charger Voltage

- Termination Enable

- Small Footprint 1-2.2µH External Inductor

Low Reverse Leakage to Prevent Battery Drain to VBUS

High Battery Discharge Efficiency With 35mΩ Battery Discharge MOSFET

High Integration Includes All MOSFETs, Current Sensing and Loop Compensation

30µA Low Battery Leakage Current to Support Ship Mode

➢ 45uA Low Battery Leakage Current in standby Mode

➢ 5V, 1A Boost Mode for USB OTG: 92% efficiency at 5V/1A

➢ QFN4x4-24L package

# 4. Pin Configuration and Functions

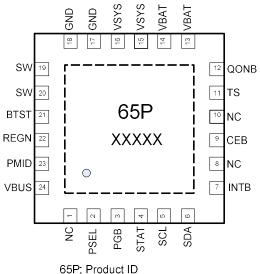

65P: Product ID XXXXX: Production Tracing Code Figure 4.1 QFN4X4-24L TOP view

## **Pin functions**

| Name | Pin #  | Туре | Description                                                                                                                                                                                                                 |

|------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBUS | 24     | Р    | Charger Input Voltage. Place a $1-\mu F$ ceramic capacitor from VBUS to GND and place it as close as possible to IC.                                                                                                        |

| -    | 1,8,10 | -    | NC.                                                                                                                                                                                                                         |

| PSEL | 2      | DI   | Power source selection input, active by PSEL_EN=1 . Set 500 mA input current limit by pulling this pin high and set input current limit by Reg00[4:0] by pulling this pin low.                                              |

| PGB  | 3      | DO   | Open drain active low power good indicator. Connect to the pull up rail through $10-k\Omega$ resistor. LOW indicates a good input source if the input voltage is between UVLO and OVP threshold, above SLEEP mode threshold |

| STAT | 4      | DO   | Open drain charge status output to indicate charger status.<br>HIGH indicates charge disabled.                                                                                                                              |

| SCL  | 5      | DI   | $I^2C$ Interface clock. Connect SCL to the logic rail through a 10-k $\Omega$ resistor.                                                                                                                                     |

| SDA  | 6      | DIO  | $I^2C$ Interface data. Connect SDA to the logic rail through a 10-k $\Omega$ resistor.                                                                                                                                      |

| INTB | 7      | DO   | Open-drain interrupt Output. The INT pin sends an pulse to host to report charger device status and fault.                                                                                                                  |

| CEB  | 9      | DI   | Charge Enable pin.<br>Battery charging is enabled when this pin is driven low.<br>Battery charging and Vsys regulator are disable when CEB is high.                                                                         |

| Name    | Pin #      | Туре                                                                     | Description                                                                          |  |  |

|---------|------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| TS      | 11         | AI                                                                       | Temperature qualification voltage input. Connect a negative temperature              |  |  |

| 10      | 11         |                                                                          | coefficient thermistor between TS and GND. 103AT-2 thermistor is preferred.          |  |  |

|         |            |                                                                          | BATFET enable/reset control input. The pin contains internal pull-up so it could be  |  |  |

|         |            |                                                                          | floating if it is not used.                                                          |  |  |

| QONB    | 12         | DI                                                                       | Pull down QONB for about 430ms will turn on BATFET and exit ship mode.               |  |  |

|         |            |                                                                          | When VBUS is not valid, a logic low of typically 10s duration cuts VSYS from         |  |  |

|         |            |                                                                          | VBAT for 430ms and then re-enables BATFET to provide full system power reset.        |  |  |

|         |            |                                                                          | Battery connection point to the positive pin of the battery pack. The internal Q4 is |  |  |

| VBAT    | 13,14      | Р                                                                        | connected between VBAT and VSYS. Connect a 22 $\mu\text{F}$ Capacitor closely to the |  |  |

|         |            |                                                                          | VBAT pin.                                                                            |  |  |

| VSYS    | 15 16      | Р                                                                        | System power supply.                                                                 |  |  |

| Vara    | 15,16      | r -                                                                      | Connect a 22 µF capacitor closely to the VBAT pin.                                   |  |  |

|         |            |                                                                          | Power ground connection for high-current power converter node. On PCB layout,        |  |  |

| GND     | 17,18      |                                                                          | connect directly to ground connection of input and output capacitors of the          |  |  |

| GND     | 17,10      | - charger. A single point connection is recommended between power PGND a |                                                                                      |  |  |

|         |            |                                                                          | analog GND near the IC PGND pin.                                                     |  |  |

| SW      | SW 19.20 P |                                                                          | Switching node connecting to output inductor. Internally SW is connected to the      |  |  |

| 300     | 19,20      |                                                                          | source of the High-side NMOS and the drain of the low-side NMOS.                     |  |  |

| BTST    | 21         | Р                                                                        | PWM high side driver positive supply. Internally, the BTST is connected to the       |  |  |

| ыы      | 21         | r -                                                                      | anode of the boost-strap diode.                                                      |  |  |

| DECN    | 22         | Р                                                                        | PWM low side driver positive supply output. Internally, REGN is connected to the     |  |  |

| REGN    | 22         | P                                                                        | cathode of the boost- strap diode.                                                   |  |  |

| DN // D | 00         | 50                                                                       | Power input to the charge regulator.                                                 |  |  |

| PMID    | 23         | DO                                                                       | Connect a 10uF ceramic capacitor from PMID to analog GND.                            |  |  |

| Thermal | Thermal    | Р                                                                        | Exposed pad for heat dissipation. Always solder thermal pad to the board, and        |  |  |

| PAD     | PAD        | Р                                                                        | have via on the thermal pad plane star-connecting to GND.                            |  |  |

**Prisemi**<sup>®</sup> Single-Cell Li-lon Switching Charger with USB-OTG Boost Regulator

# 5. Specifications

# **5.1 Maximum Ratings and Thermal Characteristics**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Parameter ( TA=                       | Symbol                | Min.              | Max. | Units              |    |

|---------------------------------------|-----------------------|-------------------|------|--------------------|----|

| VBUS Voltage                          | Continuous            | V <sub>BUS</sub>  | -0.3 | 20                 | V  |

| STAT, INTB Voltage                    |                       | V <sub>STAT</sub> | -0.3 | 7                  | V  |

| PMID                                  |                       |                   | -0.3 | 20                 |    |

| SW Voltage                            | VI                    | -0.3              | 18   | V                  |    |

| VSYS, VBAT, REGN, CEB                 |                       | -0.3              | 7    |                    |    |

| Voltage on Other Pins                 | Voltage on Other Pins |                   |      | 6.5 <sup>(1)</sup> | V  |

| Electrostatic Discharge               | Human Body Model      | ESD               | 2000 |                    | V  |

| Protection Level Charged Device Model |                       | E9D               | 50   | 00                 | V  |

| Junction Temperature                  | TJ                    | -40               | +150 | °C                 |    |

| Storage Temperature                   | Tstg                  | -65               | +150 | °C                 |    |

| Lead Soldering Temperatur             | e, 10 Seconds         | ΤL                |      | +260               | °C |

(1) Lesser of 6.5V or  $V_1$  + 0.3V.

## **5.2 Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Prisemi does not recommend exceeding them or designing to absolute maximum ratings.

| Parameter                                             | Symbol         | Min. | Max. | Units |

|-------------------------------------------------------|----------------|------|------|-------|

| Supply Voltage                                        | VBUS           | 4.5  | 13.5 | V     |

| Maximum Battery Voltage when Boost enabled            | VBAT(MAX)      |      | 4.5  | V     |

| Input Current                                         | lin            |      | 3.2  | А     |

| Output Current                                        | lsys           |      | 3    | А     |

| Fast Charging Current                                 |                |      | 3    | A     |

| Discharge Current thru internal MOSFET                |                |      | 6    | А     |

| Ambient Temperature                                   | T <sub>A</sub> | -40  | +85  | °C    |

| Junction Temperature (see Thermal Protection section) | TJ             | -40  | +140 | °C    |

## **5.3 Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_{A}$ .

| Parameter                              | Symbol          | Typical | Units        |

|----------------------------------------|-----------------|---------|--------------|

| Junction-to-Ambient Thermal Resistance | θ <sub>JA</sub> | 35      | °C <b>/W</b> |

| Junction-to-PCB Thermal Resistance     | θ <sub>JB</sub> | 10      | °C <b>/W</b> |

# **5.4 Electrical Characteristics**

Unless otherwise specified: according to the circuit of Fig.1.1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}$ =5.0V, Charge Mode; and typical values are for  $T_J$ =25°C.(Unless otherwise noted.)

| Parameter                   | Symbol             | Conditions                                                                                     | Min.  | Тур. | Max.  | Units |  |

|-----------------------------|--------------------|------------------------------------------------------------------------------------------------|-------|------|-------|-------|--|

| QUIESCENT CURRENTS          |                    |                                                                                                |       |      |       |       |  |

| VBUS Current                |                    | V <sub>BUS</sub> >V <sub>BUS(MIN)</sub> , PWM Switching<br>V <sub>BUS</sub> =12V               |       | 1.2  |       | mA    |  |

| VBUS Current                | I <sub>VBUS</sub>  | V <sub>BUS</sub> >V <sub>BUS(MIN)</sub> ; PWM Enabled,<br>Not Switching ;V <sub>BUS</sub> =12V |       | 1.2  |       | mA    |  |

| HZ Input Current            | Iнz                | HZ Mode, No Battery                                                                            |       | 660  | 800   | μA    |  |

| Battery Leakage             | Іват               | VBAT = 4.2 V, No VBUS, Not in<br>boost mode, BATFET Disabled.<br>Ta < 85°C                     |       | 30   | 40    | μA    |  |

| Battery Leakage             | Іват               | VBAT = 4.2 V, No VBUS, Not in<br>boost mode, BATFET Enabled.<br>Ta < 85°C                      |       | 45   | 58    | μA    |  |

| BATTERY CHARGER             |                    |                                                                                                |       |      |       |       |  |

| Charge Voltage Range        |                    |                                                                                                | 3.984 |      | 4.464 | V     |  |

| Charge Veltage Assurage     | VOREG              | <b>Ta=25</b> ℃                                                                                 | -0.5  |      | +0.5  | %     |  |

| Charge Voltage Accuracy     |                    | Ta=-40~85℃                                                                                     | -1    |      | 1     | %     |  |

| Output Charge Current Range |                    | VLOWV < VBAT < VOREG                                                                           |       |      | 3000  | mA    |  |

| Charge Current Accuracy     | IOCHRG             | T <sub>a</sub> <85℃,VBAT=3.8V<br>REG02[5:0]=100000,ICHG=1.92A                                  | -7.5  |      | +7.5  | %     |  |

|                             |                    | REG03[7:4]=0000                                                                                |       | 60   |       |       |  |

| Pre-charge Current          |                    | REG03[7:4]=0010                                                                                |       | 180  |       | mA    |  |

| Fie-charge Current          | IPRECHG            | REG03[7:4]=0100                                                                                |       | 300  |       |       |  |

|                             |                    | REG03[7:4]=1000                                                                                |       | 540  |       |       |  |

| Linear Charging Current     | I <sub>SHORT</sub> |                                                                                                | 15    | 20   | 25    | mA    |  |

| Battery Short Voltage       | VSHORT             |                                                                                                | 1.9   | 2.05 | 2.2   | V     |  |

| Termination Current Range   | I(TERM)            | VBAT > VOREG - VRCH                                                                            | 100   |      | 800   | mA    |  |

| Wake-up voltage Range       | Vwakeup            | Pre-Charge Current if VBAT is lower than V <sub>wakeup</sub>                                   | 2.95  | 3.1  | 3.25  | V     |  |

| VBUS Operating Voltage      | Vin_valid          | Valid VBUS voltage for charging                                                                | 4.5   |      | 13.5  | V     |  |

| VBUS Validation Time        | tvbus_valid        |                                                                                                |       | 40   |       | ms    |  |

| Parameter                                       | Symbol                | Conditions                                            | Min. | Тур. | Max. | Units |

|-------------------------------------------------|-----------------------|-------------------------------------------------------|------|------|------|-------|

| Input Voltage Regulation Range                  | VINDPM                |                                                       | 4.0  |      | 5.5  | V     |

| Input Voltage Regulation Accuracy               | VINDPM_ACC            |                                                       | -3   |      | +3   | %     |

|                                                 | V <sub>RCH</sub>      | Reg04[0]=0,Below V <sub>(OREG)</sub>                  |      | 100  |      | mV    |

| Recharge Threshold                              | t <sub>RCH</sub>      |                                                       |      | 10   |      | ms    |

| Sleep-Mode Entry Threshold, $V_{BUS} - V_{BAT}$ | VSLP                  | V <sub>BUS</sub> Falling                              |      | 100  |      | mV    |

| VBUS Over-Voltage Shutdown                      |                       | V <sub>BUS</sub> Rising (I2C programmable)            | 5.5  |      | 13.8 | V     |

| Hysteresis                                      | VBUS <sub>OVP</sub>   | V <sub>BUS</sub> Falling, VOVP=6.8V                   |      | 100  |      | mV    |

| Accuracy                                        |                       | V <sub>BUS</sub> Falling, VOVP=6.8V                   | -3   |      | +3   | %     |

| Maximum Duty Cycle (charge)                     | DMAX                  |                                                       |      |      | 98.5 | %     |

| POWER-PATH                                      |                       |                                                       |      |      |      |       |

| System regulation voltage range                 | VSYS_MIN              |                                                       | 3.2  |      | 3.7  | V     |

| System Regulation Voltage                       | VSYS_MAX              |                                                       |      | 4.5  |      | V     |

| SYS-BAT MOSFET on-resistance                    | RON(Q4)               |                                                       |      | 35   |      | mΩ    |

| Q3 On Resistance (VBUS to PMID)                 |                       | I <sub>IN(LIMIT)</sub> =500mA                         |      | 45   |      |       |

| Q1 On Resistance (PMID to SW)                   | R <sub>DS(ON)</sub>   |                                                       |      | 60   |      | mΩ    |

| Q2 On Resistance (SW to GND)                    |                       |                                                       |      | 60   |      |       |

| BOOST MODE OPERATION                            |                       |                                                       |      |      |      | 1     |

| Boost Output Voltage at VBUS                    | VBOOST                | 3.3V <v<sub>BAT&lt;4.5V;</v<sub>                      | 4.8  | 5.15 | 5.3  | V     |

| Boost Mode Quiescent Current                    | IBAT(BST)             | PFM Mode, V <sub>BAT</sub> =4.2V, I <sub>OUT</sub> =0 |      | 1.7  |      | mA    |

| Valley Cyment Lineit (O4)                       |                       | Reg02[7]=0                                            |      | 0.8  |      | А     |

| Valley Current Limit (Q1)                       | I <sub>LIM(BST)</sub> | Reg02[7]=1                                            |      | 1.5  |      | А     |

| Current Limit (Q4)                              | ILIM(BAT)             |                                                       |      | 3.0  |      | Α     |

| Min Battery Voltage for Boost                   | UVLOBST               |                                                       |      | 3.2  |      | V     |

| LOGIC I/O PIN CHARACTERISTICS                   |                       |                                                       |      |      |      |       |

| High-Level Input Voltage                        | VIH                   |                                                       | 1.2  |      |      | V     |

| Low-Level Input Voltage                         | VIL                   |                                                       |      |      | 0.4  | V     |

| STAT Output Low                                 | V <sub>STAT(OL)</sub> | I <sub>STAT</sub> =10mA                               |      |      | 0.4  | V     |

| STAT High Leakage Current                       | Istat(oh)             | V <sub>STAT</sub> =5V                                 |      |      | 1    | μA    |

| THERMAL SHUTDOWN                                |                       |                                                       |      |      |      |       |

| Thermal Shutdown Threshold <sup>(1)</sup>       | Т                     | T <sub>J</sub> Rising                                 |      | 145  |      | °C    |

| Hysteresis <sup>(4)</sup>                       | - Tshutdwn            | TJ Falling                                            |      | 10   |      | °C    |

(1) Guaranteed by design; not tested in production.

| Parameter                                                  | Symbol       | Conditions | Min. | Тур.  | Max. | Units |

|------------------------------------------------------------|--------------|------------|------|-------|------|-------|

| JEITA Thermistor Comparator (BUCK                          | (MODE)       |            |      |       |      | •     |

| Cold (0°C) threshold                                       | T4           |            |      | 73.30 |      |       |

| Falling                                                    | - T1         |            |      | 71.50 |      |       |

| Cool (10°C) threshold,                                     |              |            |      | 68.00 |      |       |

| Falling                                                    | - T2<br>- T3 |            |      | 66.80 |      |       |

| Warm (45°C) threshold,                                     |              |            |      | 44.70 |      | %     |

| Falling                                                    |              |            |      | 45.70 |      |       |

| Hot (60°C) threshold,                                      |              |            |      | 34.20 |      |       |

| Falling                                                    | T5           |            |      | 35.30 |      |       |

| Timing for QONB (external Key)                             | 1            |            | 1    | 1     |      | 1     |

| QONB time to full system reset;<br>BATFET switch on-off-on | Tqon_rst2    |            |      | 10    |      | s     |

| BATFET's off time during full system reset                 | Tqon_off     |            |      | 40    |      | ms    |

| QONB low time to exit ship mode                            | Tship_exit   |            |      | 160   |      | ms    |

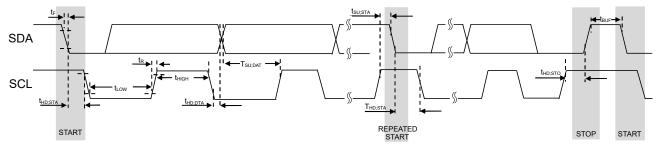

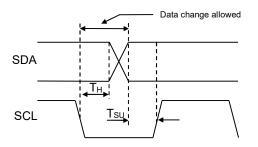

# 5.5 I2C Timing Specifications

Guaranteed by design.

| Parameter                                     | Symbol              | Conditions    | Min. | Тур.              | Max. | Units |

|-----------------------------------------------|---------------------|---------------|------|-------------------|------|-------|

|                                               | fscL                | Standard Mode |      |                   | 100  | kHz   |

| SCL Clock Frequency                           |                     | Fast Mode     |      |                   | 400  | КПД   |

| Bus-Free Time between STOP                    | tBUF                | Standard Mode |      | 4.7               |      |       |

| and START Conditions                          |                     | Fast Mode     |      | 1.3               |      | μs    |

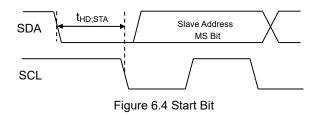

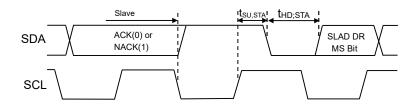

| START or Repeated START                       | thd:sta             | Standard Mode |      | 4                 |      | μs    |

| Hold Time                                     | LHD;STA             | Fast Mode     |      | 600               |      | ns    |

| SOL LOW/Devied                                |                     | Standard Mode |      | 4.7               |      |       |

| SCL LOW Period                                | t∟ow                | Fast Mode     |      | 1.3               |      | μs    |

|                                               |                     | Standard Mode |      | 4                 |      | μs    |

| SCL HIGH Period                               | tніgн               | Fast Mode     |      | 600               |      | ns    |

|                                               |                     | Standard Mode |      | 4.7               |      | μs    |

| Repeated START Setup Time                     | t <sub>su;sta</sub> | Fast Mode     |      | 600               |      | ns    |

| Data Oatur Tiraa                              | 4                   | Standard Mode |      | 250               |      |       |

| Data Setup Time                               | tsu;dat             | Fast Mode     |      | 100               |      | ns    |

| Data Hald Time                                | 4                   | Standard Mode | 0    |                   | 3.45 | μs    |

| Data Hold Time                                | t <sub>hd;dat</sub> | Fast Mode     | 0    |                   | 900  | ns    |

|                                               |                     | Standard Mode | 20+0 | ).1Св             | 1000 |       |

| SCL Rise Time                                 | t <sub>RCL</sub>    | Fast Mode     | 20+0 | 0.1Св             | 300  | ns    |

|                                               |                     | Standard Mode | 20+0 | ).1C <sub>в</sub> | 300  |       |

| SCL Fall Time                                 | t <sub>FCL</sub>    | Fast Mode     | 20+0 | ).1Св             | 300  | ns    |

| SDA Rise Time<br>Rise Time of SCL after a     | t <sub>RDA</sub>    | Standard Mode | 20+0 | ).1C <sub>в</sub> | 1000 |       |

| Repeated START Condition<br>and after ACK Bit | t <sub>RCL1</sub>   | Fast Mode     | 20+0 | ).1Cв             | 300  | ns    |

| Parameter                    | Symbol           | Conditions    | Min.                 | Тур. | Max. | Units |

|------------------------------|------------------|---------------|----------------------|------|------|-------|

| SDA Fall Time                | <b>+</b>         | Standard Mode | 20+0.1C <sub>B</sub> |      | 300  | ns    |

|                              | t <sub>FDA</sub> | Fast Mode     | 20+0.1C <sub>B</sub> |      | 300  |       |

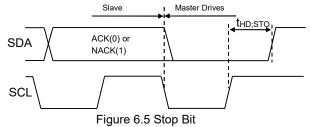

|                              | tsu;s⊤o          | Standard Mode |                      | 4    |      | μs    |

| Stop Condition Setup Time    |                  | Fast Mode     |                      | 600  |      | ns    |

| Capacitive Load for SDA, SCL | C <sub>B</sub>   |               |                      |      | 400  | pF    |

Figure 5.1 I<sup>2</sup>C Interface Timing for Fast and Slow Modes

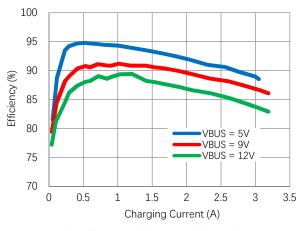

# **5.6 Typical Performance Plots**

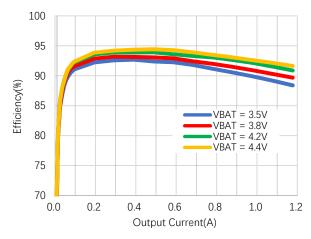

Fig1. Charge Efficiency vs. Charge Current

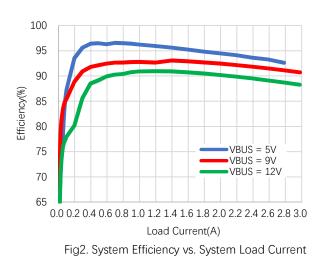

Fig3. Boost Mode Efficiency vs. VBUS Load Current

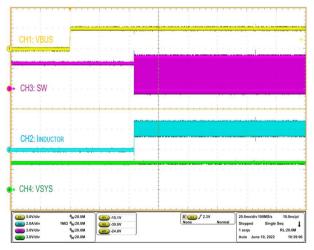

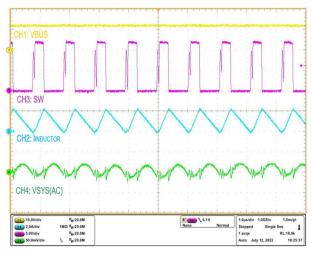

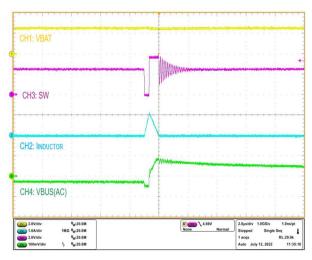

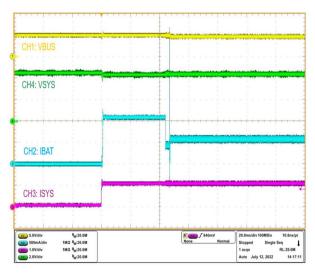

Fig5. Power on (VBAT=3.8V,lcharge=2A)

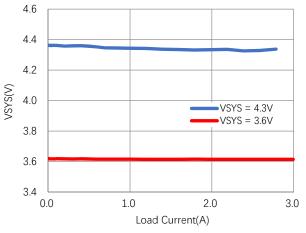

Fig4. VSYS Voltage Regulation vs. System Load Current

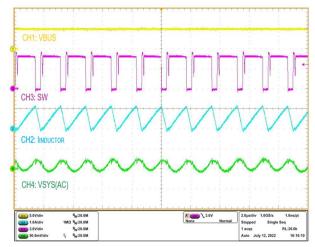

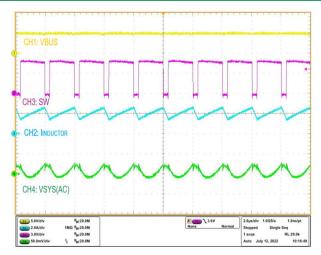

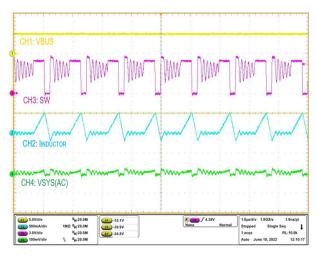

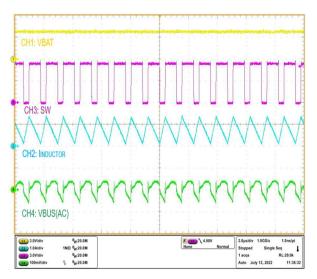

Fig6. Switching in Buck Mode (Vbus=5V,Icharge=500mA)

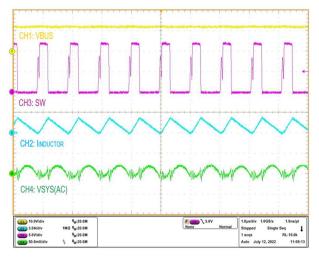

Fig7. Switching in Buck Mode (Vbus=5V,lcharge=1A)

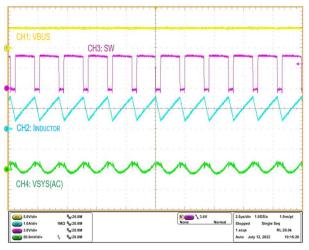

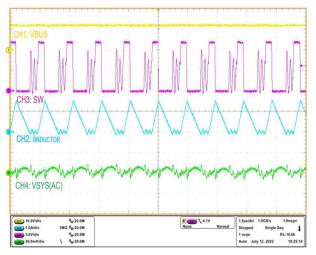

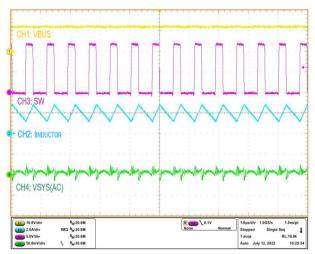

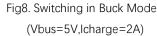

Fig9. Switching in Buck Mode (Vbus=12V,Icharge=500mA)

Fig11. Switching in Buck Mode (Vbus=12V,Icharge=2A)

Fig10. Switching in Buck Mode (Vbus=12V,Icharge=1A)

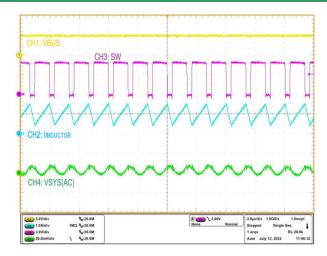

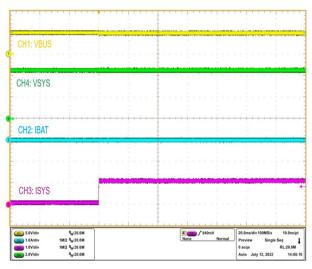

Fig12. VSYS Operation (Vbus=5V,Vsys=3.6V,Isys=No Load)

Fig13. VSYS Operation (Vbus=5V,Vsys=3.6V,Isys=100mA)

Fig15. VSYS Operation (Vbus=12V,Vsys=3.6V,Isys=1A)

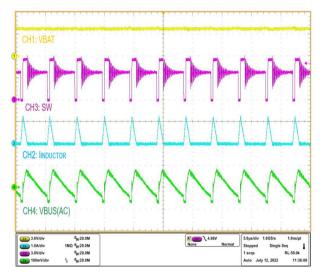

Fig17. OTG switching (Vbat=3.8V,Vbus=5.3V,Iload=100mA)

Fig14. VSYS Operation (Vbus=5V,Vsys=3.6V,Isys=1A)

Fig16. OTG Switching (Vbat=3.8V,Vbus=5.3V,No Load)

Fig18. OTG switching (Vbat=3.8V,Vbus=5.3V,Iload=500mA)

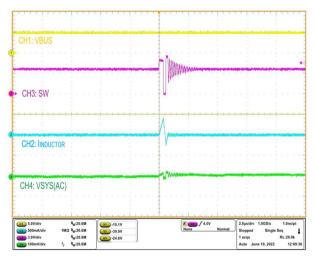

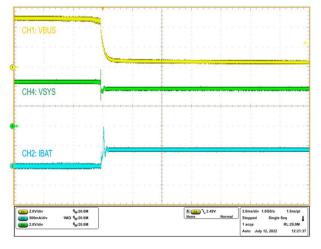

Fig19. System Load Transient

(Input is not over load, ISYS is only supported from BUS )

Fig21. System Load Transient

(Q4 turn on, ISYS supported from BAT after BUS input remove )

Fig20. System Load Transient

(Input is over load, ISYS is supported from both BUS and BAT)

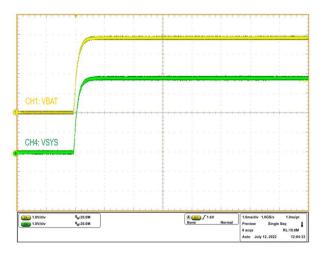

Fig22. System Start up from Battery (No Load, VBUS Float)

# 6. Detailed Description

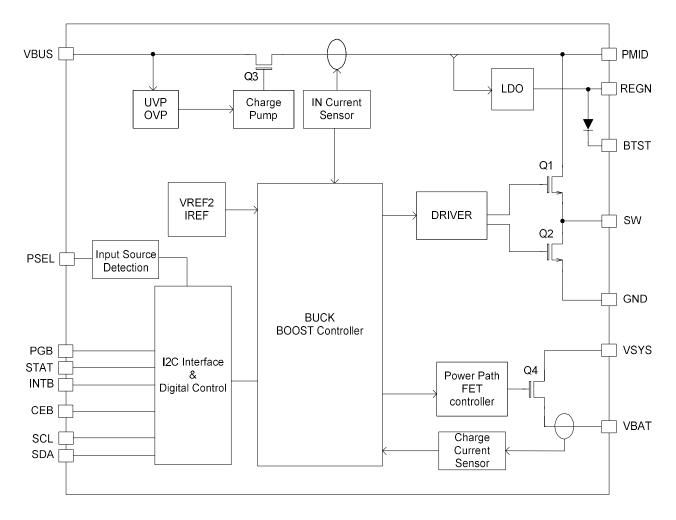

## 6.1 Circuit Overview

The PSC2965 is an I2C controlled power path management device and a single cell Li-Ion battery charger. It integrates the input reverse-blocking FET (RBFET, Q3), high-side switching FET (HSFET, Q1), low-side switching FET (LSFET, Q2), and battery FET (BATFET, Q4) between system and battery. The device also integrates the bootstrap diode for the high-side gate drive.

## 6.2 Function Block Diagram

Figure 6.1 Block Diagram

### 6.3 Feature Description

## 6.3.1 Power Up from Battery without DC Source

When VBAT is powered up, the BATFET turns on and connects battery to system. The low RDSON in BATFET and the low quiescent current on BAT minimize the conduction loss and maximize the battery run time..

# 6.3.2 Interrupt to Host (INTB)

In some applications, the host does not always monitor the charger operation. The INT pulse notifies the systems on the device operation. The following events will generate 300us INT pulse.

- USB/adapter insertion and remove

- Charge complete

- NTC cold or hot detect

- 32s watchdog timer expire

- BAT temperature become abnormal or return to normal.

When a fault occurs, the charger device sends out INT and keeps the fault state in REG09 until all the faults are cleared. Before all the faults are cleared, the charger device would not send any INT upon new faults.

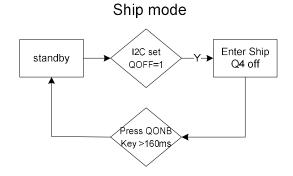

## 6.3.3 Shipping Mode

#### 6.3.3.1 Enter Ship Mode

To extend battery life and minimize power when system is powered off during system idle, shipping, or storage, the device can turn off BATFET so that the system voltage is zero to minimize the leakage. The BATFET can be turned off by setting QOFF bit to "1".

- Setting REG07[5](QOFF) to "1" allows the user to turn off the BATFET when the IC doesn't work in charging mode and boost mode, but reset REG07[5] to "0" is invalid.

- In charging mode and boost mode, setting REG07[5] to "1" is invalid, but the BATFET can be turned off when VBAT is fully charged.

#### 6.3.3.2 Exit Ship Mode

When the BATFET is disabled (in shipping mode) and indicated by setting QOFF, one of the following events can enable BATFET to restore system power:

1. Plug in adapter

2. Reset all by write "1" to REG0B[7];

3. A logic high to low transition on QONB pin with tSHIPMODE deglitch time to enable BATFET to exit shipping mode.

### 6.3.4 Power Path Management

### 6.3.4.1 Narrow VDC Architecture

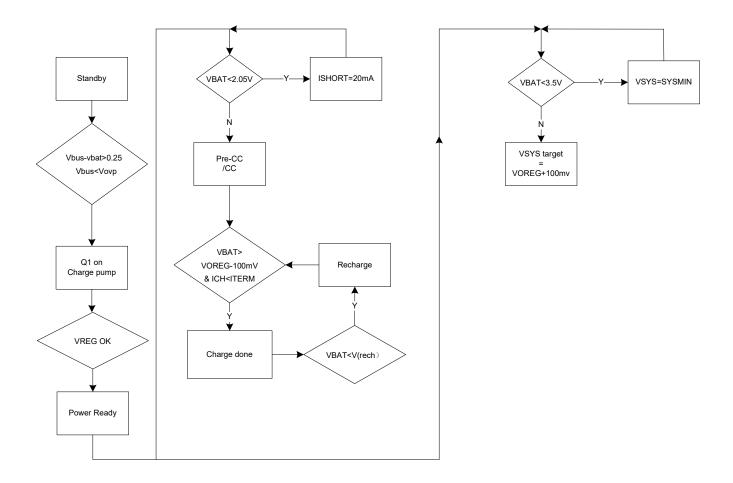

The device deploys Narrow VDC architecture (NVDC) with BATFET separating system from battery. The minimum system voltage is set by REG01[3:1]. Even with a fully depleted battery, the system is regulated above the minimum system voltage (default 3.5 V).

When the battery is below minimum system voltage setting, the BATFET operates in linear mode (LDO mode), and the system is regulated at the minimum system voltage. As the battery voltage rises to Vsysmin-100mv, BATFET is fully turned on in switch mode.

When the battery is fully charged, the system is regulated at about VOREG+100mV.

### 6.3.4.2 Dynamic Power Management

To meet maximum current limit in USB spec and avoid over loading the adapter, the device features Dynamic Power Management (DPM), which continuously monitors the input current and input voltage.

When input source is over-loaded, either the current exceeds the input current limit or the voltage falls below the input voltage limit. The device then reduces the charge current until the input current falls below the input current limit and the input voltage rises above the input voltage limit.

When the charge current is reduced to zero, but the input source is still overloaded, the device automatically enters the supplement mode. Battery starts discharging so that the system is supported from both the input source and battery.

#### **PSC2965**

#### Single-Cell Li-Ion Switching Charger with USB-OTG Boost Regulator

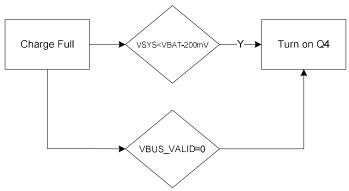

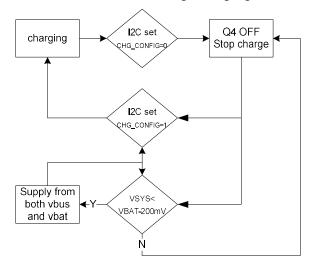

### Charge done during system on

Turn off Q4 during charging

Force system reset

## 6.3.5 Charge Mode

### 6.3.5.1 Four Regulation Loops

1. Charging Current: Limits the maximum charging current. This current is sensed using internal BATFET.

2. Charge Voltage: The regulator is restricted from exceeding this voltage. As the internal battery voltage rises, the battery's internal impedance and BATFET work in conjunction with the charge voltage regulation to decrease the amount of current flowing to the battery. Battery charging is completed when the current thru BATFET drops below the I<sub>TERM</sub> threshold.

3. Input Current: Limits the amount of current drawn from VBUS. This current is sensed internally and can be programmed through the I<sup>2</sup>C interface.

4. Input Voltage: PSC2965 employ an additional loop to limit the amount of drop on VBUS to a programmable voltage ( $V_{SP}$ ) to accommodate "special chargers" that limit current to a lower current than might be available from a "normal" USB wall charger.

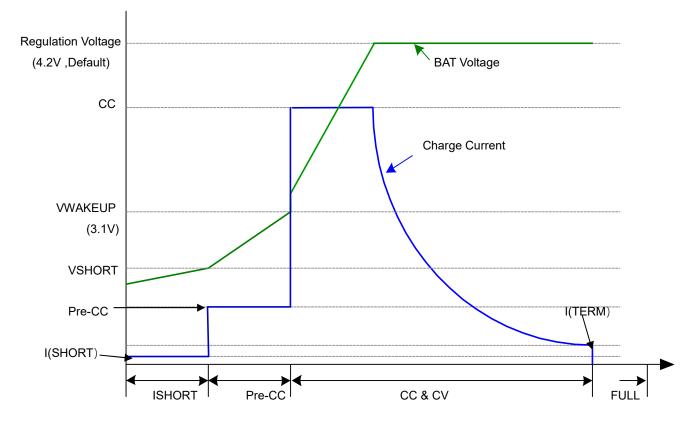

### 6.3.5.2 Battery Charging Curve

The device charges the battery in four phases: activating, preconditioning, constant current, Fast-CC and constant voltage.

#### **Charging Current Setting**

| VBAT                                                       | Charging Phase | Setting REG |

|------------------------------------------------------------|----------------|-------------|

| VBAT < VSHORT<br>(Typical 2.05V)                           | ISHORT         | -           |

| VSHORT ≤ VBAT < VWAKEUP<br>(Typical 2.05 V ≤ VBAT < 3.1 V) | Pre-CC         | REG03[7:4]  |

| VWAKEUP≤ VBAT<br>(Typical 3.1V ≤ VBAT < Voreg)             | СС             | REG02[5:0]  |

Note: If the charger device is in DPM regulation during charging, the actual charging current will be less than the programmed value.

Figure 6.2 Charge Curve, ICHARGE Not Limited by IINLIM

### 6.3.5.3 Charge Termination

The device terminates a charge cycle when the battery voltage is above recharge threshold, and the current is below termination current. After the charging cycle is complete, the BATFET turns off. The converter keeps running to power the system, and BATFET can turn back on to engage supplement mode. When termination occurs, the status register REG08[4:3] is 11. Termination can be disabled by writing 0 to REG05[7].

The host can disable charging and VSYS power through CEB pin, or set REG01[4] to 0.Setting QOFF (REG07[5]) from 0 to 1 will cut VSYS from VBAT so as to disable charging, which won't impact VSYS supply.

#### 6.3.5.4 Charger Safety Timer

The charger has a time out function for normal charge. For normal charging the timer is set to 12 hours. If the charger is still operating after typical 12 hours, BATFET will be turned OFF and will be turned on if the condition (VOREG-VBAT) >100mV is met, or plugging out the adapter. The 12-hour timer can be reset by plugging out/in the adapter.

### 6.3.5.5 Charging Status Indicator (STAT)

The device indicates charging state on the open drain STAT pin. The STAT pin can drive LED as the application diagram shows.

|               | STAT |

|---------------|------|

| VBUS is valid | LOW  |

| NO valid VBUS | HIGH |

### 6.3.5.6 Thermal Shutdown

During charge operation, the device monitors the internal junction temperature T<sub>J</sub> to avoid overheat the chip and limits the IC surface temperature. When the internal junction temperature exceeds 140°C, the device is disabled, and is enabled if junction temperature lower than 120°C.

### 6.3.5.7 Input Over-Voltage Detection

When the VBUS exceeds VBUS<sub>OVP</sub>, the IC suspends charging. When VBUS falls a hysteresis voltage below VBUS<sub>OVP</sub>, the fault is cleared and charging resumes after VBUS is revalidated.

### 6.3.5.8 Battery Short Protection

If the battery voltage falls below  $V_{short}$  (2.4V typical), the device will turn off BATFET and keep 20mA linear charging current to VBAT.

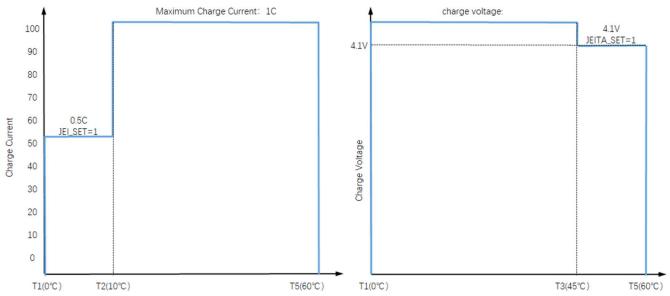

### 6.3.5.9 JEITA

JEITA Guideline Compliance During Charging Mode

To improve the safety of charging Li-ion batteries, JEITA guideline was released on April 20, 2007. The guideline emphasized the importance of avoiding a high charge current and high charge voltage at certain low and high temperature ranges.

To initiate a charge cycle, the voltage on TS pin must be within the VT1 to VT5 thresholds. If TS voltage exceeds the T1-T5 range, the controller suspends charging and waits until the battery temperature is within the T1 to T5 range.

At cool temperature (T1-T2), JEITA recommends the charge current to be reduced to half of the charge current or lower. At warm temperature (T3-T5), JEITA recommends charge voltage less than 4.1 V.

The charger provides flexible voltage/current settings beyond the JEITA requirement. The voltage setting at warm temperature (T3-T5) can be VOREG or 4.1V (configured by JEITA\_SET). The current setting at cool temperature (T1-T2) can be further reduced to 50% of fast charge current (JEITA\_SET).

Note: 103AT as thermistor.

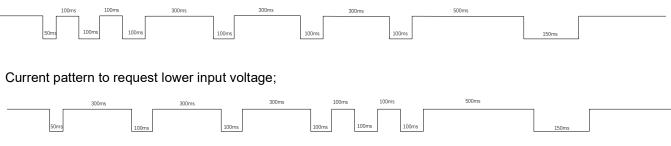

### 6.3.5.10 Current Pulse Modulation

The device includes interface to support adjustable high voltage adapter using input current pulse protocol.

Current pattern to request higher input voltage.

Current pulse can be programmed directly by control DIS\_PWM(REGA0[7]).

## 6.3.6 Charger Parameters Description

Assuming that  $V_{OREG}$  is programmed to the cell's fully charged "float" voltage, the current that the battery accepts with the PWM regulator limiting its output (sensed at VBAT) to  $V_{OREG}$  declines, and the charger enters the voltage regulation phase of charging. When the current declines to the programmed I<sub>TERM</sub> value, the charge cycle is complete. Charge current termination can be disabled by setting the TE bit (REG1[3]). The charger output or "float" voltage can be programmed by the OREG bits from 3.6V to 4.45V as shown in REG02[6:4].

®

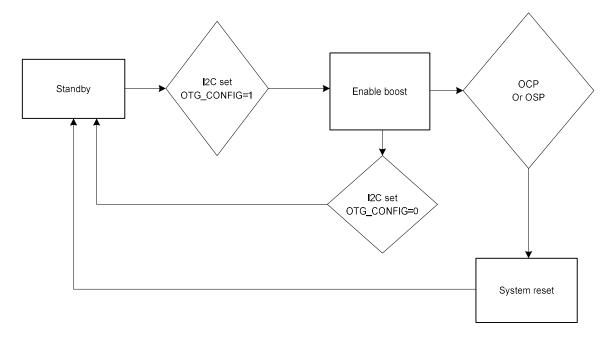

## 6.3.7 BOOST Mode

Prisemi

Boost Mode can be enabled by setting ENBOOST=1 through I2C. If there is valid VBUS, boost converter will be suspended.

#### 6.3.7.1 Startup

When the boost regulator is shut down, current flow is prevented from  $V_{BAT}$  to  $V_{BUS}$ , as well as reverse flow from  $V_{BUS}$  to  $V_{BAT}$ .

### 6.3.7.2 Soft Start

This IC has built-in soft start function to prevent the IC being out of control. The reference voltage is slightly raised to the normal voltage within about 100us.

#### 6.3.7.3 BST State

This is the normal operating mode of the regulator. The regulator uses a cot modulation scheme. The minimum  $t_{OFF}$  is proportional to  $\frac{V_{IN}}{V_{OUT}}$  Which keeps the regulator's switching frequency reasonably constant in CCM.

To ensure the VBUS does not pump significantly above the regulation point, the boost switch remains off as long as FB >  $V_{REF}$ .

### 6.3.7.4 Over Current Protection

The device monitors the BATFET current to ensure safe boost mode operation. If over-current condition is detected, the device will lower the output voltage first. After about 400us, if it's still in over-current conditions, the device will reset and quit boost mode.

### 6.3.8 I2C Interface

The PSC2965's serial interface is compatible with Standard, Fast, Fast Plus, and High-Speed Mode I<sup>2</sup>C-Bus® specifications. The PSC2965's SCL line is an input and its SDA line is a bi-directional open-drain output; it can only pull down the bus when active. The SDA line only pulls LOW during data reads and when signaling ACK. All data is shifted in MSB (bit 7) first.

#### **Slave Address**

The hex slave address for the PSC2965 is D6H.

#### **Bus Timing**

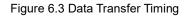

As shown in Figure 6.3, data is normally transferred when SCL is LOW. Data is clocked in on the rising edge of SCL. Typically, data transitions shortly at or after the falling edge of SCL to allow ample time for the data to set up before the next SCL rising edge.

Each bus transaction begins and ends with SDA and SCL HIGH. A transaction begins with a START condition, which is defined as SDA transitioning from 1 to 0 with SCL HIGH, as shown in Figure 6.4.

A transaction ends with a STOP condition, which is defined as SDA transitioning from 0 to 1 with SCL HIGH, as shown in Figure 6.5.

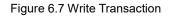

During a read from the PSC2965, the master issues a Repeated Start after sending the register address and before resending the slave address. The Repeated Start is a 1-to-0 transition on SDA while SCL is HIGH, as shown in Figure 6.6.

Figure 6.6 Repeated Start Timing

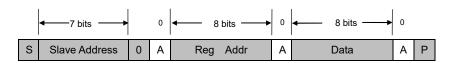

#### **Read and Write Transactions**

The figures below outline the sequences for data read and write. Bus control is signified by the shading of the packet, defined

as Master Drives Bus and Slave Drives Bus

All addresses and data are MSB first.

#### Bit Definitions for Figure 6.7, Figure 6.8

| Symbol | Definition                                                          |

|--------|---------------------------------------------------------------------|

| S      | START, see Figure 6.4                                               |

| A      | ACK. The slave drives SDA to 0 to acknowledge the preceding packet. |

| Ā      | NACK. The slave sends a 1 to NACK the preceding packet.             |

| R      | Repeated START, see Figure 6.6                                      |

| Р      | STOP, see Figure 6.5                                                |

Figure 6.8 Read Transaction

#### **Register Descriptions**

#### Reg00

| Bit | Field     | POR | Туре  | Reset       | Description             | Comment                          |

|-----|-----------|-----|-------|-------------|-------------------------|----------------------------------|

| 7   | EN_HIZ    | 0   | R/W   | by REG_RST  | 0 – Disable, 1 – Enable | Enable HIZ Mode                  |

| 1   |           | 0   |       | by Watchdog |                         | 0 – Disable (default) 1 – Enable |

| 6   | Reserved  | 0   | R/W   | by REG_RST  | Reserved                | Reserved                         |

| 0   | Reserved  | 0   |       | by Watchdog | Reserved                | i ved                            |

| 5   | Reserved  | 0   | R/W   | by REG_RST  | Reserved                | Reserved                         |

| 5   | Reserved  | 0   | r//// | by Watchdog | Reserveu                | Reserved                         |

| 4   | IINDPM[4] | 1   | R/W   | by REG_RST  | 1600 mA                 | Current Limit Offset: 100 mA     |

| 3   | IINDPM[3] | 0   | R/W   | by REG_RST  | 800 mA                  | Range: 100 mA (000000) – 3.2 A   |

| 2   | IINDPM[2] | 1   | R/W   | by REG_RST  | 400 mA                  | (1111)                           |

| 1   | IINDPM[1] | 1   | R/W   | by REG_RST  | 200 mA                  | Default:                         |

|     |           |     |       |             |                         | PSEL=Hi, 500mA (00100)           |

|     |           |     |       |             |                         | PSEL=Lo,2400mA (10111),          |

|     |           |     |       |             |                         | maximum input current limit, not |

| 0   | IINDPM[0] | 1   | R/W   | by REG_RST  | 100 mA                  | typical.                         |

| 0   |           |     |       | by REG_ROT  |                         | Host can't set current limit by  |

|     |           |     |       |             |                         | writing IINDPM register bits     |

|     |           |     |       |             |                         | when PSEL=H and PSEL_EN=1        |

|     |           |     |       |             |                         | (See description in Reg07[1]).   |

| Bit | Field          | POR | Туре       | Reset       | Description                            | Comment                        |

|-----|----------------|-----|------------|-------------|----------------------------------------|--------------------------------|

| 7   | Reserve        | 0   | R/W        | by REG_RST  | Reserved                               | Reserved                       |

| '   |                | U   | 11/00      | by Watchdog |                                        |                                |

| 6   | WD RST         | 0   | R/W        | by REG_RST  | 0 - Normal ;                           | Default: Normal (0) Back to 0  |

| 0   |                | U   | 1 1/ 1     | by Watchdog | 1 - Reset                              | after watchdog timer reset     |

|     |                |     |            |             |                                        | Default: OTG disable (0) Note: |

| 5   | OTG CONFIG     | 0   | R/W        | by REG_RST  | 0 – OTG Disable                        | 1. OTG_CONFIG would            |

| 5   |                | U   |            | by Watchdog | 1 – OTG Enable                         | over-ride Charge Enable        |

|     |                |     |            |             |                                        | Function in CHG_CONFIG         |

|     |                |     |            |             |                                        | Default: Charge Battery (1)    |

|     |                |     |            | W DEC DET   | 0 Chargo Disable                       | Note:                          |

| 4   | CHG_CONFIG     | 1   | R/W        |             | 0 - Charge Disable<br>1- Charge Enable | 1. Charge is enabled when both |

|     |                |     |            | by watchdog | I- Charge Enable                       | CE pin is pulled low and       |

|     |                |     |            |             |                                        | CHG_CONFIG bit is 1.           |

| 3   | SYS_Min[2]     | 1   | R/W        | by REG_RST  |                                        | 000-011: 3.2V                  |

| 2   | SYS_Min[1]     | 0   | R/W        | by REG_RST  |                                        | 100: 3.4 V                     |

|     |                |     |            |             | System Minimum Voltage                 | 101: 3.5 V                     |

|     | 0)/0 Min [0]   | 4   |            |             |                                        | 110: 3.6 V                     |

| 1   | 1 SYS_Min[0] 1 | R/W | by REG_RST |             | 111: 3.7 V                             |                                |

|     |                |     |            |             |                                        | Default: 3.5 V (101)           |

| 0   | Posonuod       |     | 0 R/W      | by REG_RST  | Peserved                               | Percentred                     |

| U   | Reserved       | 0   | r(/V)      | by Watchdog | Reserved                               | Reserved                       |

| Reg02 | 2         |     |      |                           |             |                                                                                                 |

|-------|-----------|-----|------|---------------------------|-------------|-------------------------------------------------------------------------------------------------|

| Bit   | Field     | POR | Туре | Reset                     | Description | Comment                                                                                         |

| 7     | BOOST_LIM | 1   | R/W  | by REG_RST<br>by Watchdog |             | Default: 1.5 A (1) Note:<br>The current limit options listed<br>are valley current limit specs. |

| 6     | Reserved  | 0   | R/W  | by REG_RST<br>by Watchdog | Reserved    | Reserved                                                                                        |

| 5     | ICHG[5]   | 1   | R/W  | by REG_RST<br>by Watchdog | 1920 mA     |                                                                                                 |

| 4     | ICHG[4]   | 0   | R/W  | by REG_RST<br>by Watchdog | 960 mA      | Fast Charge Current Default:<br>2040mA (100010)                                                 |

| 3     | ICHG[3]   | 0   | R/W  | by REG_RST<br>by Watchdog | 480 mA      | ——Range: 0 mA (0000000) – 3000<br>mA (110010)<br>——Note:                                        |

| 2     | ICHG[2]   | 0   | R/W  | by REG_RST<br>by Watchdog | 240 mA      | I <sub>CHG</sub> = 0 mA disables charge.<br>I <sub>CHG</sub> > 3000 mA (110010                  |

| 1     | ICHG[1]   | 1   | R/W  | by REG_RST<br>by Watchdog | 120 mA      | clamped to register value 3000<br>mA (110010))                                                  |

| 0     | ICHG[0]   | 0   | R/W  | by REG_RST<br>by Watchdog | 60 mA       |                                                                                                 |

| Bit | Field      | POR | Туре | Reset                     | Description | Comment                                                          |

|-----|------------|-----|------|---------------------------|-------------|------------------------------------------------------------------|

| 7   | IPRECHG[3] | 0   | R/W  | by REG_RST<br>by Watchdog | 480 mA      |                                                                  |

| 6   | IPRECHG[2] | 0   | R/W  | by REG_RST<br>by Watchdog | 240 mA      | Precharge Current Default:<br>180 mA (0010)                      |

| 5   | IPRECHG[1] | 1   | R/W  | by REG_RST<br>by Watchdog | 120 mA      | -Offset: 60 mA<br>Special Value:<br>-1111: 0mA,disable precharge |

| 4   | IPRECHG[0] | 0   | R/W  | by REG_RST<br>by Watchdog | 60 mA       |                                                                  |

| 3   | ITERM[3]   | 0   | R/W  | by REG_RST<br>by Watchdog | 800 mA      |                                                                  |

| 2   | ITERM[2]   | 0   | R/W  | by REG_RST<br>by Watchdog | 400 mA      | Termination Current Default:<br>300 mA (0010)                    |

| 1   | ITERM[1]   | 1   | R/W  | by REG_RST<br>by Watchdog | 200 mA      | ─Offset: 100 mA<br>Maximum termination current :<br>─800mA(1000) |

| 0   | ITERM[0]   | 0   | R/W  | by REG_RST<br>by Watchdog | 100 mA      |                                                                  |

| Bit | Field           | POR | Туре | Reset                     | Description                          | Comment                                                                                |

|-----|-----------------|-----|------|---------------------------|--------------------------------------|----------------------------------------------------------------------------------------|

| 7   | VREG[4]         | 0   | R/W  | by REG_RST<br>by Watchdog | 512 mV                               | Charge Voltage Offset:<br>3.856V                                                       |

| 6   | VREG[3]         | 1   | R/W  | by REG_RST<br>by Watchdog | 256 mV                               | Special Value:<br>00000-00011: 3.984 V<br>Range: 3.984V to 4.464 V                     |

| 5   | VREG[2]         | 0   | R/W  | by REG_RST<br>by Watchdog | 128 mV                               | (11000)<br>Default: 4.208 V (01011)                                                    |

| 4   | VREG[1]         | 1   | R/W  | by REG_RST<br>by Watchdog | 64 mV                                | Special Value:<br>11000 -11111: 4.464V                                                 |

| 3   | VREG[0]         | 1   | R/W  | by REG_RST<br>by Watchdog | 32 mV                                | Clamped to register value<br>11000 (4.464 V)                                           |

| 2   | TOPOFF_TIMER[1] | 0   | R/W  | by REG_RST<br>by Watchdog | 00 – Disabled (Default)<br>01 – 150s | The extended time following the termination condition is met.<br>When disabled, charge |

| 1   | TOPOFF_TIMER[0] | 0   | R/W  | by REG_RST<br>by Watchdog |                                      | terminated when termination<br>conditions are met                                      |

| 0   | VRECHG          | 0   | R/W  | by REG_RST<br>by Watchdog |                                      | Recharge threshold Default:<br>100mV (0)                                               |

| Reg0 |                         |     |        |             |                           |                                 |

|------|-------------------------|-----|--------|-------------|---------------------------|---------------------------------|

| Bit  | Field                   | POR | Туре   | Reset       | Description               | Comment                         |

| 7    |                         | 1   | R/W    | by REG_RST  | 0 – Disable               | Default: Enable termination (1) |

| 1    | EN_TERM                 |     | r./vv  | by Watchdog | 1 – Enable                | Default: Enable termination (1) |

| 6    | Reserved                | 0   | R/W    | by REG_RST  | Reserved                  | Reserved                        |

| 0    | Reserved                | 0   | r./vv  | by Watchdog | Reserved                  | Reserveu                        |

| 5    | Deserved                | 0   | R/W    | by REG_RST  | Reserved                  | Deconved                        |

| 5    | Reserved                | 0   | rt/VV  | by Watchdog | Reserved                  | Reserved                        |

| 4    |                         | 1   | R/W    | by REG_RST  | Reserved                  | Reserved                        |

| 4    | Reserved                | I   |        | by Watchdog | Reserved                  |                                 |

| 3    |                         | 1   | R/W by | by REG_RST  | 0 – Disable               | Default: Enable (1)             |

| 3    | WD_EN                   |     | r(/vv  | by Watchdog | 1 – Enable watchdog timer | Default: Enable (1)             |

| 2    | Deserved                | 1   | R/W    | by REG_RST  | Reserved                  | Deconved                        |

| 2    | Reserved                | 1   | rt/VV  | by Watchdog | Reserved                  | Reserved                        |

|      | December                |     |        | by REG_RST  | December                  |                                 |

| 1    | Reserved                | 1   | R/W    | by Watchdog | Reserved                  | Reserved                        |

| 0    |                         |     |        | by REG_RST  | 0 – 50% of ICHG           |                                 |

| U    | 0 JEITA_ISET (0C-10C) 1 | 1   | R/W    | by Watchdog | 1 – 20% of ICHG           | Default: 20%                    |

| Bit | Field     | POR | Туре    | Reset      | Description        | Comment                     |            |            |

|-----|-----------|-----|---------|------------|--------------------|-----------------------------|------------|------------|

| 7   | OVP[1]    | 0   | R/W     | by REG_RST |                    | VAC OVP threshold:          |            |            |

|     |           |     |         |            |                    | 00 - 5.5 V                  |            |            |

| 6   | OVP[0]    | 1   |         | by REG RST | Default: 6.8V (01) | 01 – 6.8 V (5-V input)      |            |            |

| 0   | Ovrioj    | I   | FX/ V V | DY REG_ROI |                    | 10 – 11 V (9-V input)       |            |            |

|     |           |     |         |            |                    | 11 – 13.8 V (12-V input)    |            |            |

| 5   | BOOSTV[1] | 1   | R/W     | by REG_RST |                    | Boost Regulation Voltage:   |            |            |

|     |           |     |         | by REG_RST |                    | 00 - 4.85V                  |            |            |

| 4   |           | 0   |         |            |                    | 01 - 5.00V                  |            |            |

| 4   | BOOSTV[0] | 0   | R/W     |            |                    | by REG_RST                  |            | 10 - 5.15V |

|     |           |     |         |            |                    |                             | 11 - 5.30V |            |

| 3   | VINDPM[3] | 0   | R/W     | by REG_RST | 800 mV             | Absolute VINDPM Threshold   |            |            |

| 2   | VINDPM[2] | 1   | R/W     | by REG_RST | 400 mV             | Offset: 4.0 V               |            |            |

| 1   | VINDPM[1] | 1   | R/W     | by REG_RST | 200 mV             | Range: 4.0 V (0000) – 5.5 V |            |            |

| 0   |           | _   |         | W DEC DET  | 100 m)/            | (1111)                      |            |            |

| 0   | VINDPM[0] | 0   | r./ v v | by REG_RST | 100 mV             | Default: 4.6V (0110)        |            |            |

| Bit | Field                   | POR | Туре | Reset                     | Description                                                                                                                                                 | Comment                                                                                                                    |

|-----|-------------------------|-----|------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 7   | PSEL_EN                 | 0   | R/W  | by REG_RST<br>by Watchdog | 1 - Enable<br>0 - Disable                                                                                                                                   | Default: Disable PSEL(0)<br>PSEL_EN=1:<br>IINLIM=500mA@PSEL = Hi;<br>IINLIM is determined by the<br>Reg 00[4:0]@ PSEL = Lo |

| 6   | Reserved                | 0   | R/W  | by REG_RST<br>by Watchdog | Reserved                                                                                                                                                    | Reserved                                                                                                                   |

| 5   | BATFET_DIS              | 0   | R/W  | by REG_RST                | 0-Allow Q4 turn on,<br>1-Turn off Q4 with t <sub>BATFET_DLY</sub><br>delay time (REG07[3])                                                                  | Default: Allow Q4 turn on(0)                                                                                               |

| 4   | JEITA_VSET<br>(45C-60C) | 0   | R/W  | by REG_RST<br>by Watchdog | 0-Set Charge Voltage to 4.1V<br>( max),<br>1-Set Charge Voltage to VREG                                                                                     |                                                                                                                            |

| 3   | BATFET_DLY              | 1   | R/W  | by REG_RST                | 0-Turn off BATFET immediately<br>when BATFET_DIS bit is set<br>1-Turn off BATFET after<br>t <sub>BATFET_DLY</sub> (typ. 10 s) when<br>BATFET_DIS bit is set | Default: 1<br>Turn off BATFET after t <sub>BATFET_DLY</sub><br>(typ. 10 s) when BATFET_DIS<br>bit is set                   |

| 2   | BATFET_RST_EN           | 1   | R/W  | by REG_RST<br>by Watchdog | 0-Disable BATFET reset<br>function<br>1-Enable BATFET reset function                                                                                        | Default: 1<br>Enable BATFET reset function                                                                                 |

| 1   | VDPM_BAT_TRACK[1]       | 0   | R/W  | by REG_RST                | 00- Disable function (VINDPM                                                                                                                                | Sets VINDPM to track BAT                                                                                                   |

| 0   | VDPM_BAT_TRACK[0]       | 0   | R/W  |                           | set by register)<br>01- VBAT + 240mV<br>10- VBAT + 260mV<br>11- VBAT + 300mV                                                                                | voltage. Actual VINDPM is<br>higher of register value and<br>VBAT + VDPM_BAT_TRACK                                         |

| Reg08 | Reg08        |     |      |                                                                                  |                                                                                                              |  |  |  |  |

|-------|--------------|-----|------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit   | Field        | POR | Туре | Reset                                                                            | Description                                                                                                  |  |  |  |  |

| 7     | VBUS_STAT[2] | х   | R    | NA                                                                               | VBUS Status register 000: No input or in Boost mode                                                          |  |  |  |  |

| 6     | VBUS_STAT[1] | х   | R    | NA                                                                               | 001: USB Host SDP (500 mA)                                                                                   |  |  |  |  |

| 5     | VBUS_STAT[0] | x   | R    | 010: Adapter 2.4A<br>NA<br>Software current limit is reported in IINDPM register |                                                                                                              |  |  |  |  |

| 4     | CHRG_STAT[1] | х   | R    | NA                                                                               | Charging status: By monitoring the voltage of battery                                                        |  |  |  |  |

| 3     | CHRG_STAT[0] | x   | R    | NA                                                                               | 00 -Not Charging<br>01 - Pre-charge (< V <sub>BATLOWV</sub> )<br>10 -Fast Charging<br>11 -Charge Termination |  |  |  |  |

| 2     | PG_STAT      | x   | R    | NA                                                                               | Power Good status:<br>0 – Power Not Good<br>1 – Power Good                                                   |  |  |  |  |

| 1     | THERM_STAT   | x   | R    | NA                                                                               | 0 – Not in thermal regulation; 1 – in thermal regulation                                                     |  |  |  |  |

| 0     | VSYS_STAT    | x   | R    | NA                                                                               | 0 – Not in VSYSMIN regulation (BAT > VSYSMIN)<br>1 – in VSYSMIN regulation (BAT < VSYSMIN)                   |  |  |  |  |

#### Reg09

| Bit | Field          | POR | Туре | Reset          | Description                                                                                                        |

|-----|----------------|-----|------|----------------|--------------------------------------------------------------------------------------------------------------------|

| 7   | WATCHDOG_FAULT | х   | R    | NA             | 0 – Normal, 1- Watchdog timer expiration                                                                           |

| 6   | BOOST_FAULT    | x   | R    | NA             | 0 – Normal, 1 – VBUS overloaded in OTG, or battery is too low (any conditions that we cannot start boost function) |

| 5   | CHRG_FAULT[1]  | х   | R    | NA             | 00 – Normal, 01 – input fault (OVP) or Thermal shutdown                                                            |

| 4   | CHRG_FAULT[0]  | х   | R    | NA             | 11 – Charge Safety Timer Expiration                                                                                |

| 3   | Reserved       | х   | R    | NA             |                                                                                                                    |

| 2   | NTC_FAULT[2]   | х   | R    | NA             | JEITA                                                                                                              |

| 1   | NTC_FAULT[1]   | х   | R    | NA             | 000 – Normal, 010 – Warm, 011 – Cool, 101 – Cold, 110 – Hot                                                        |

| 0   | NTC_FAULT[0]   | x   | R    | NA (Buck mode) |                                                                                                                    |

PSC2965

| Reg0/ | Reg0A       |     |      |       |                                          |  |

|-------|-------------|-----|------|-------|------------------------------------------|--|

| Bit   | Field       | POR | Туре | Reset | Description                              |  |

| 7     | VBUS_GD     | x   | R    | NA    | 0 – Not VBUS attached, 1 – VBUS Attached |  |

| 6     | VINDPM_STAT | х   | R    | NA    | 0 – Not in VINDPM, 1 – in VINDPM         |  |

| 5     | IINDPM_STAT | x   | R    | NA    | 0 – Not in IINDPM, 1 – in IINDPM         |  |

| 4:0   | Reserved    | х   | R    | NA    |                                          |  |

#### Reg0B

| Bit | Field      | POR | Туре | Reset | Description                                                                                                                                                                  |

|-----|------------|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | REG_RST    | 0   | R/W  | NA    | Register reset<br>0 – Keep current register setting<br>1 – Reset to default register value and reset safety timer Note: Bit<br>resets to 0 after register reset is completed |

| 6   | PN[3]      | 0   | R    | NA    |                                                                                                                                                                              |

| 5   | PN[2]      | 0   | R    | NA    |                                                                                                                                                                              |

| 4   | PN[1]      | 1   | R    | NA    |                                                                                                                                                                              |

| 3   | PN[0]      | 0   | R    | NA    |                                                                                                                                                                              |

| 2   | Reserved   | 0   | R    | NA    |                                                                                                                                                                              |

| 1   | DEV_REV[1] | 0   | R    | NA    |                                                                                                                                                                              |

| 0   | DEV_REV[0] | 0   | R    | NA    |                                                                                                                                                                              |

#### Reg0C

| Bit | Field   | POR | Туре | Reset                 | Description                                                |

|-----|---------|-----|------|-----------------------|------------------------------------------------------------|

|     |         |     |      | 0:Enable NTC(default) |                                                            |

|     |         | 0   |      | by REG_RST            | 1:Disable NTC                                              |

| 4   | NTC_DIS | 0   | R/W  | by Watchdog           | Note: The NTC_DIS must be set to 1 for high current(>2.0A) |

|     |         |     |      |                       | applications.                                              |

#### Reg0D

| Bit | Field                | POR | Туре | Reset | Description                                                 |

|-----|----------------------|-----|------|-------|-------------------------------------------------------------|

| 7:6 | Charge Current Limit |     | R/W  |       | 10:for Icharge<=2.0A<br>11:No charge current limit          |

| 0   | Thermal_DIS          | 0   | R/W  |       | 0:Enable Thermal Regulation<br>1:Disable Thermal Regulation |

# 7. PCB Layout Guidelines

The switching node rise and fall times should be minimized for minimum switching loss. Proper layout of the components to minimize high frequency current path loop (see Figure 7.1) is important to prevent electrical and magnetic field radiation and high frequency resonant problems. Here is a PCB layout priority list for proper layout. Layout PCB according to this specific order is essential.

1. Place input capacitor as close as possible to PMID pin and GND pin connections and use shortest copper trace connection or GND plane.

2. Place inductor input pin to SW pin as close as possible. Minimize the copper area of this trace to lower electrical and magnetic field radiation but make the trace wide enough to carry the charging current. Do not use multiple layers in parallel for this connection. Minimize parasitic capacitance from this area to any other trace or plane.

3. Put output capacitor near to the inductor and the IC. Ground connections need to be tied to the IC ground with a short copper trace connection or GND plane.

4. Route analog ground separately from power ground. Connect analog ground and connect power ground separately. Connect analog ground and power ground together using thermal pad as the single ground connection point. Or using a  $0\Omega$  resistor to tie analog ground to power ground.

5. Use single ground connection to tie charger power ground to charger analog ground. Just beneath the IC. Use ground copper pour but avoid power pins to reduce inductive and capacitive noise coupling.

6. Decoupling capacitors should be placed next to the IC pins and make trace connection as short as possible.

7. It is critical that the exposed thermal pad on the backside of the IC package be soldered to the PCB ground.

Ensure that there are sufficient thermal vias directly under the IC, connecting to the ground plane on the other layers.

8. The via size and number should be enough for a given current path.

Figure 7.1 high frequency current path

# 8. Package Information

#### COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN   | NOM   | MAX   |

|--------|-------|-------|-------|

| Α      | 0.700 | 0.750 | 0.820 |

| A1     | 0.000 | /     | 0.050 |

| A2     | 0.153 | 0.203 | 0.273 |

| b      | 0.200 | 0.250 | 0.300 |

| D      | 3.900 | 4.000 | 4.100 |

| D1     | 2.600 | 2.700 | 2.800 |

| E      | 3.900 | 4.000 | 4.100 |

| E1     | 2.600 | 2.700 | 2.800 |

| е      | 0.450 | 0.500 | 0.550 |

| h      | 0.200 | 0.250 | 0.300 |

| k      | 0.150 | 0.250 | 0.350 |

| L      | 0.350 | 0,400 | 0.450 |

#### **Ordering Information**

| Device  | Package              | Reel | Shipping           |  |

|---------|----------------------|------|--------------------|--|

| PSC2965 | QFN4x4-24L (Pb-Free) | 13"  | 5000 / Tape & Reel |  |

#### IMPORTANT NOTICE